本文介绍: 高电平时间占(M/2) * T_sys_clk, 在这个期间有(M>>1)个完整的sys_clk + 半个sys_clk.低电平时间占(M/2) * T_sys_clk, 在这个期间有(M>>1)个完整的sys_clk + 半个sys_clk.高电平时间占(N/2) * T_sys_clk,在这个期间有N/2个sys_clk系统时钟。低电平时间占(N/2) * T_sys_clk,在这个期间有N/2个sys_clk系统时钟。灵活使用计数器,可以进行分频。实现任意整数奇偶分频。

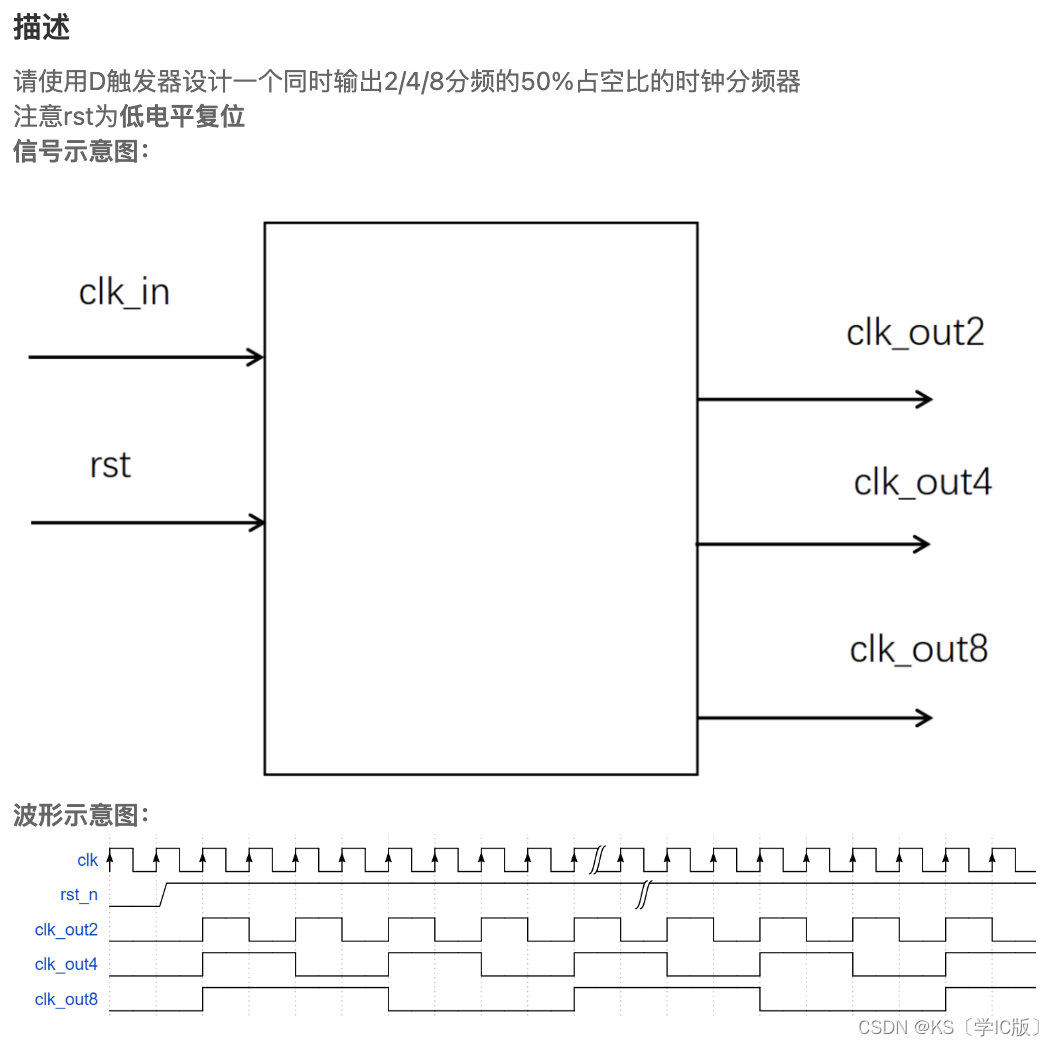

实验目标:

/*

二分频电路就是用同一个时钟信号通过一定的电路结构转变成不同频率的时钟信号。

二分频就是通过有分频作用的电路结构,在时钟每触发2个周期时,电路输出1个周期信号。

比如用一个脉冲时钟触发一个计数器,计数器每计2个数就清零一次并输出1个脉冲。

四分频就是通过有分频作用的电路结构,在时钟每触发4个周期时,电路输出1个周期信号。

比如用一个脉冲时钟触发一个计数器,计数器每计4个数就清零一次并输出1个脉冲,

*/

需求分析:

高电平时间占(N/2) * T_sys_clk,在这个期间有N/2个sys_clk系统时钟。

低电平时间占(N/2) * T_sys_clk,在这个期间有N/2个sys_clk系统时钟。

高电平时间占(M/2) * T_sys_clk, 在这个期间有(M>>1)个完整的sys_clk + 半个sys_clk.

低电平时间占(M/2) * T_sys_clk, 在这个期间有(M>>1)个完整的sys_clk + 半个sys_clk.

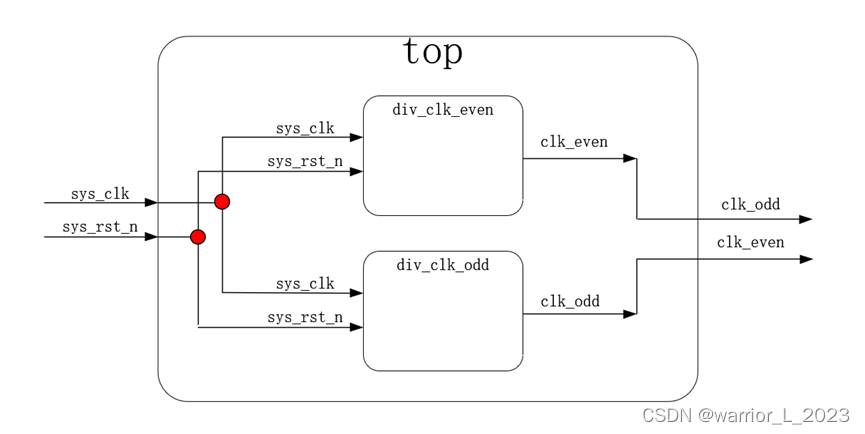

模块框图:

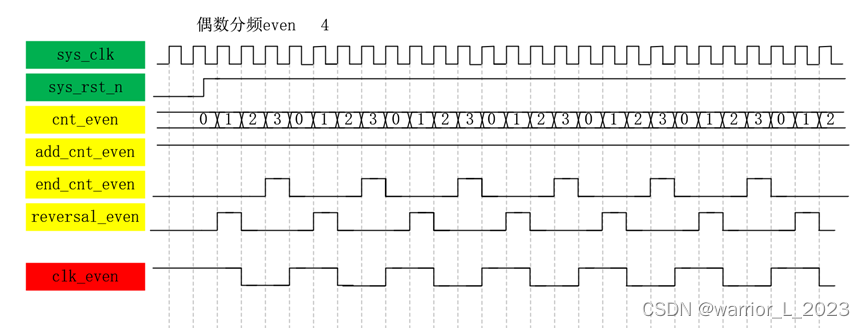

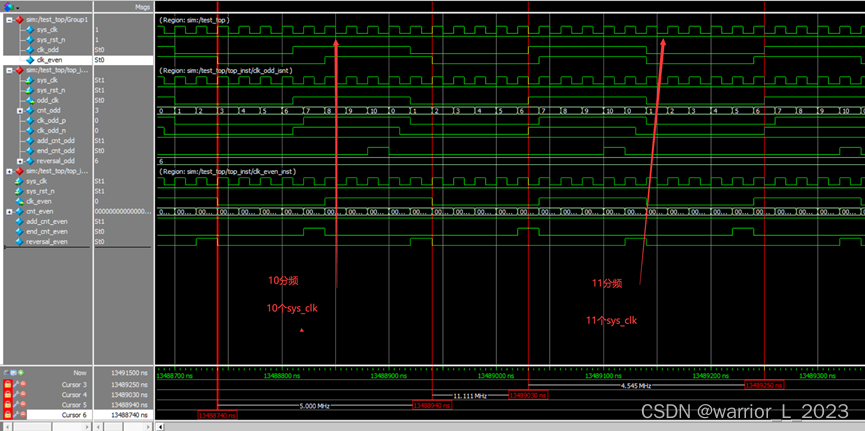

时序图:

代码:

/*

二分频电路就是用同一个时钟信号通过一定的电路结构转变成不同频率的时钟信号。

二分频就是通过有分频作用的电路结构,在时钟每触发2个周期时,电路输出1个周期信号。

比如用一个脉冲时钟触发一个计数器,计数器每计2个数就清零一次并输出1个脉冲。

那么这个电路就实现了二分频功能。

四分频就是通过有分频作用的电路结构,在时钟每触发4个周期时,电路输出1个周期信号。

比如用一个脉冲时钟触发一个计数器,计数器每计4个数就清零一次并输出1个脉冲,

那么这个电路就实现了四分频功能。

*/

module top (

input wire sys_clk ,

input wire sys_rst_n ,

output wire clk_even ,

output wire clk_odd

);

clk_even clk_even_inst(

.sys_clk ( sys_clk ) ,

.sys_rst_n ( sys_rst_n ) ,

.clk_even ( clk_even )

);

clk_odd clk_odd_isnt(

.sys_clk ( sys_clk ) ,

.sys_rst_n ( sys_rst_n ) ,

.odd_clk ( clk_odd )

);

endmodule/*

奇数分频。整数。

*/

`include "para.v"

module clk_odd (

input wire sys_clk ,

input wire sys_rst_n ,

output wire odd_clk

);

// reg signal

reg [31:0] cnt_odd ;

reg clk_odd_p ;

reg clk_odd_n ;

// wire signal

wire add_cnt_odd ;

wire end_cnt_odd ;

wire [31:0] reversal_odd;

/******************************************************************************************

********************************************main code**************************************

*******************************************************************************************/

// reg signal

// reg [31:0] cnt_odd ;

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n)

cnt_odd <= 32'd0 ;

else if(add_cnt_odd) begin

if(end_cnt_odd)

cnt_odd <= 32'd0 ;

else

cnt_odd <= cnt_odd + 1'b1 ;

end

else

cnt_odd <= 32'd0 ;

end

// reg clk_odd_p ;

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n)

clk_odd_p <= 1'b0 ;

else if(cnt_odd >= reversal_odd)

clk_odd_p <= 1'b1 ;

else

clk_odd_p <= 1'b0 ;

end

// reg clk_odd_n ;

always @(negedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n)

clk_odd_n <= 1'b0 ;

else if(cnt_odd >= reversal_odd)

clk_odd_n <= 1'b1 ;

else

clk_odd_n <= 1'b0 ;

end

// wire signal

// wire add_cnt_odd ;

assign add_cnt_odd = 1'b1 ;

// wire end_cnt_odd ;

assign end_cnt_odd = add_cnt_odd && (cnt_odd == (`ODD_NUM - 1)) ;

// wire reversal_odd;

assign reversal_odd= ((`ODD_NUM >> 1) + 1) ; // 由于加的优先级大于>> 所以要加括号。

// output wire odd_clk

assign odd_clk = clk_odd_p || clk_odd_n ;

endmodule/*

偶数分频。整数。

*/

`include "para.v"

module clk_even (

input wire sys_clk ,

input wire sys_rst_n ,

output reg clk_even

);

// reg signal

reg [31:0] cnt_even ;

// wire signal

wire add_cnt_even ;

wire end_cnt_even ;

wire reversal_even ;

/******************************************************************************************

********************************************main code**************************************

*******************************************************************************************/

// // reg signal

// reg [31:0] cnt_even ;

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n)

cnt_even <= 32'd0 ;

else if(add_cnt_even) begin

if(end_cnt_even)

cnt_even <= 32'd0 ;

else

cnt_even <= cnt_even + 1'b1 ;

end

else

cnt_even <= 32'd0 ;

end

// // wire signal

// wire add_cnt_even ;

assign add_cnt_even = 1'b1 ;

// wire end_cnt_even ;

assign end_cnt_even = add_cnt_even && (cnt_even == (`EVEN_NUM - 1)) ;

// wire reversal_even ;

assign reversal_even= (cnt_even == ((`EVEN_NUM >> 1) - 1)) ;

// output reg clk_even

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n)

clk_even <= 1'b1 ;

else if(reversal_even || end_cnt_even)

clk_even <= ~clk_even ;

else

clk_even <= clk_even ;

end

endmodule`timescale 1ns/1ns

module test_top ();

reg sys_clk ;

reg sys_rst_n ;

wire clk_odd ;

wire clk_even ;

parameter CYCLE = 20 ;

top top_inst(

.sys_clk ( sys_clk ) ,

.sys_rst_n ( sys_rst_n ) ,

.clk_even ( clk_even ) ,

.clk_odd ( clk_odd )

);

initial begin

sys_clk = 1'b1 ;

sys_rst_n <= 1'b0 ;

#(CYCLE * 2) ;

sys_rst_n <= 1'b1 ;

end

always #(CYCLE/2) sys_clk = ~sys_clk ;

endmodule

原文地址:https://blog.csdn.net/Meng_long2022/article/details/134751883

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:http://www.7code.cn/show_31768.html

如若内容造成侵权/违法违规/事实不符,请联系代码007邮箱:suwngjj01@126.com进行投诉反馈,一经查实,立即删除!

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。