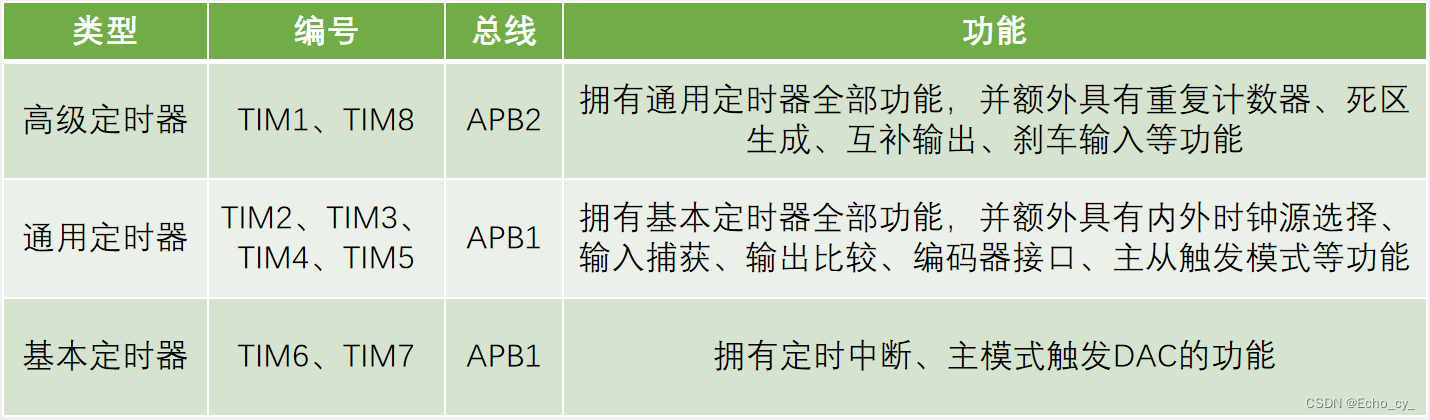

本文介绍: 在STM32中,定时器起着至关重要的作用,它设计复杂但功能强大,针对不同的情境有严谨的设计。TIM(Timer)定时器定时器可以对输入的时钟进行计数,并在计数值达到设定值时触发中断。16位计数器、预分频器、自动重装寄存器的时基单元,在72MHz计数时钟下可以实现最大59.65s的定时定时器不仅具备基本的定时中断功能,而且还包含内外时钟源选择、输入捕获、输出比较、编码器接口、主从触发模式等多种功能根据复杂度和应用场景分为了高级定时器、通用定时器、基本定时器三种类型。

前言

在STM32中,定时器起着至关重要的作用,它设计复杂但功能强大,针对不同的情境有严谨的设计。

一、TIM简介

定时器就是一个计数器,当这个计数器的输入是一个准确可靠的基准时钟的时候。那它在对这个基准时钟进行计数的过程实际上就是计时的过程。在STM32中,定时器的基准时钟一般都是主频72MHz,如果对72MHz计72个数,是1MHz也就是1us 的时间;如果计72000个数,是1KHz也就是1ms的时间。

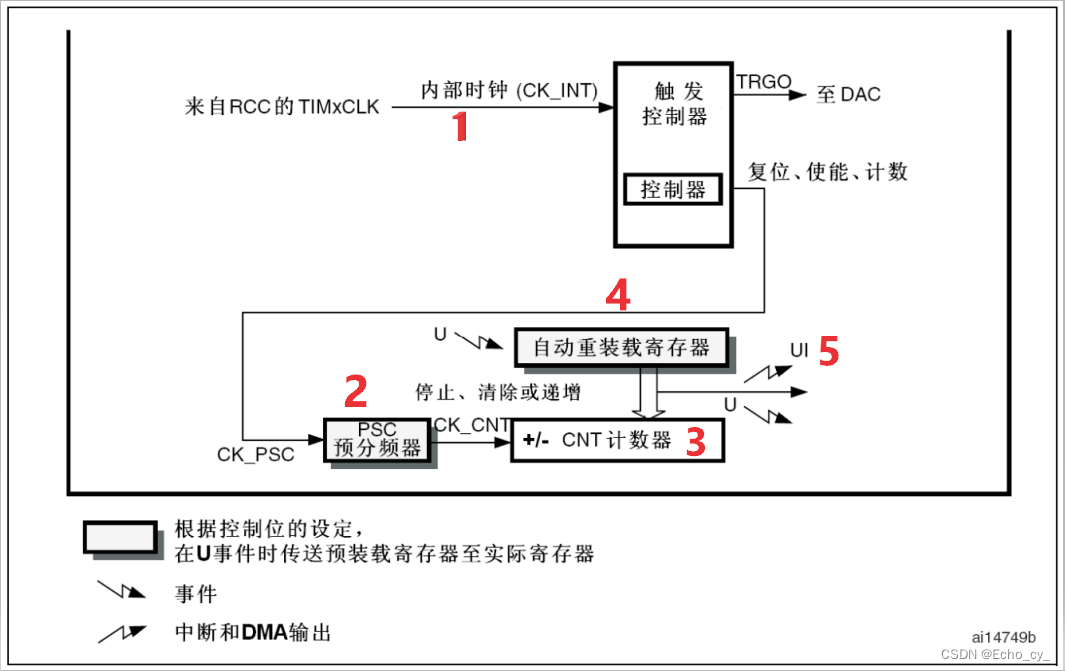

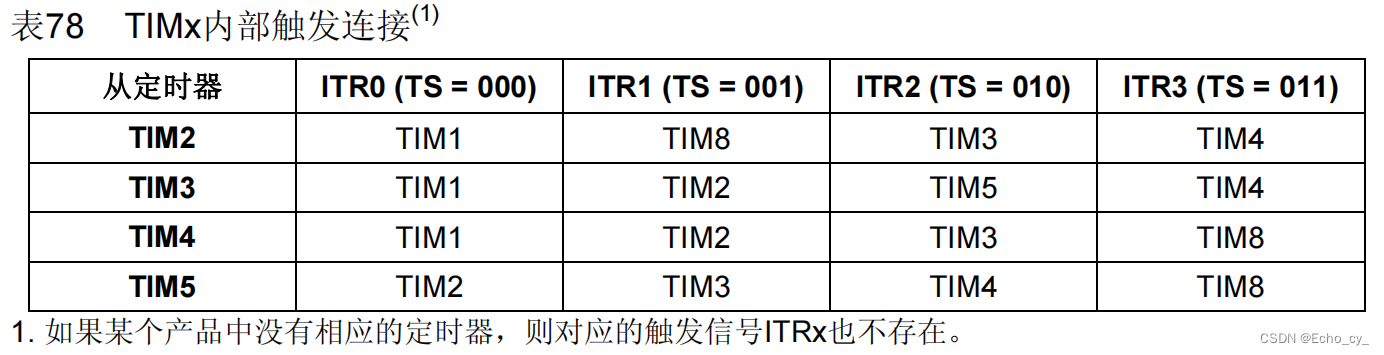

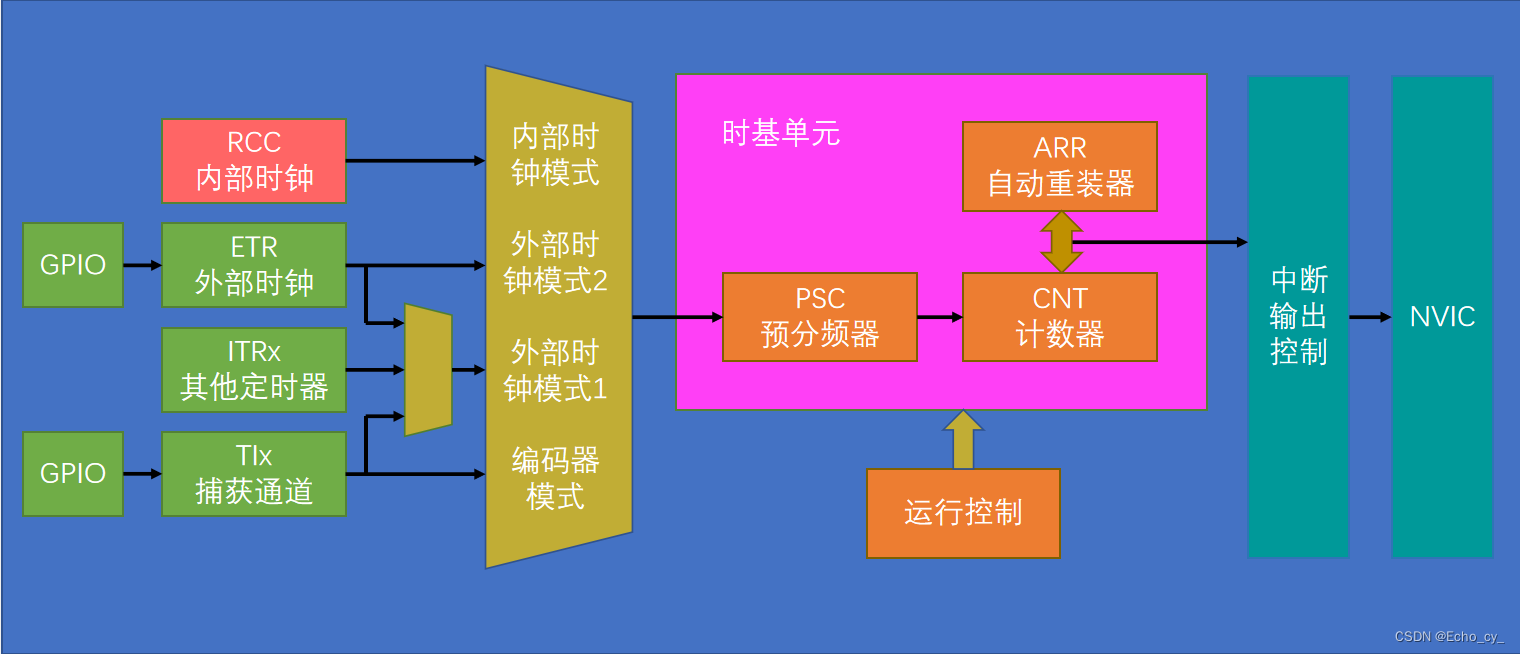

这三个寄存器构成了定时器最核心的部分,这一块电路称为时基单元。时基单元里的计数器、预分频器、自动重装寄存器都是16位的,2的16次方是65536,也就是如果预分频器设置最大,自动重装寄存器也设置最大,那定时器的最大定时时间就是59.65s,接近一分钟。STM32的定时器还支持级联的模式,也就是一个定时器的输出,当作另一个定时器的输入。这样加一起,最大定时时间就是59.65s×65536×65536,这个时间大概是八千多年。

二、STM32的三种定时器

2.1基本定时器

2.1.1定时中断功能

1. 时钟源

2. 预分频器

3. 计数器

4. 自动重装寄存器

5.更新中断和更新事件

2.1.2主模式触发DAC功能

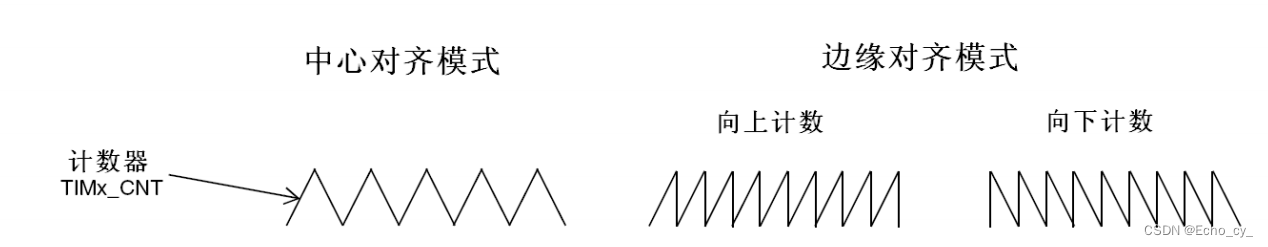

2.2 计数模式

2.2通用定时器

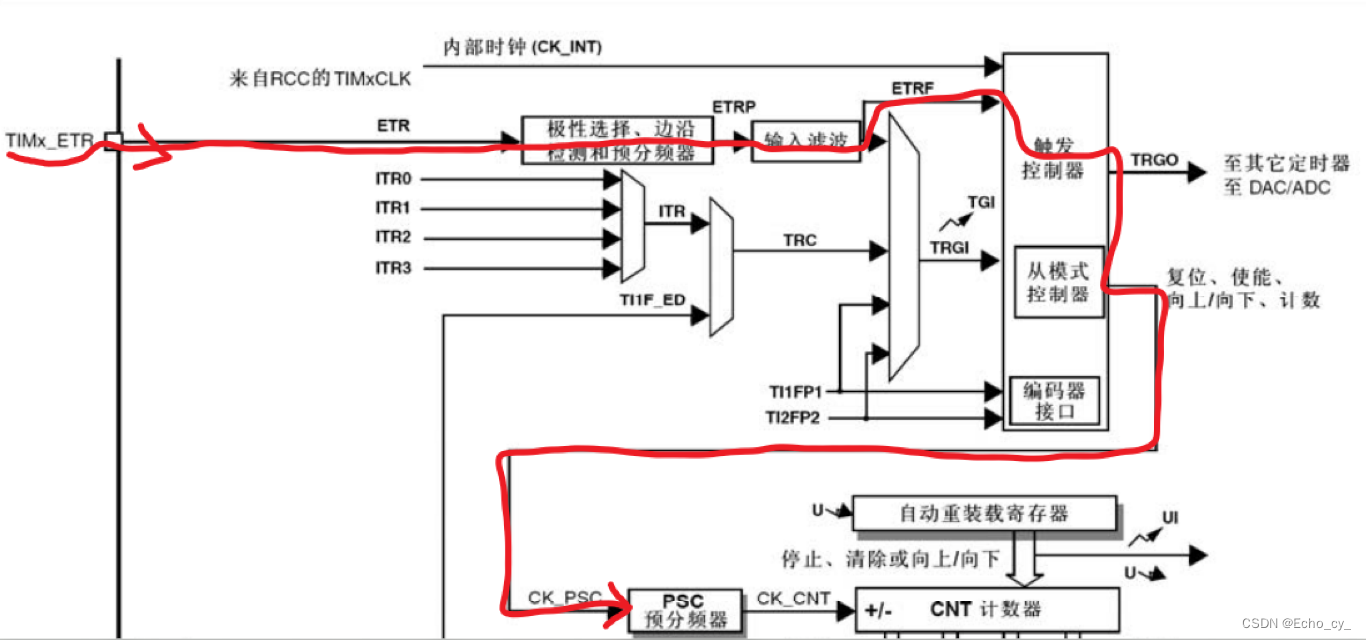

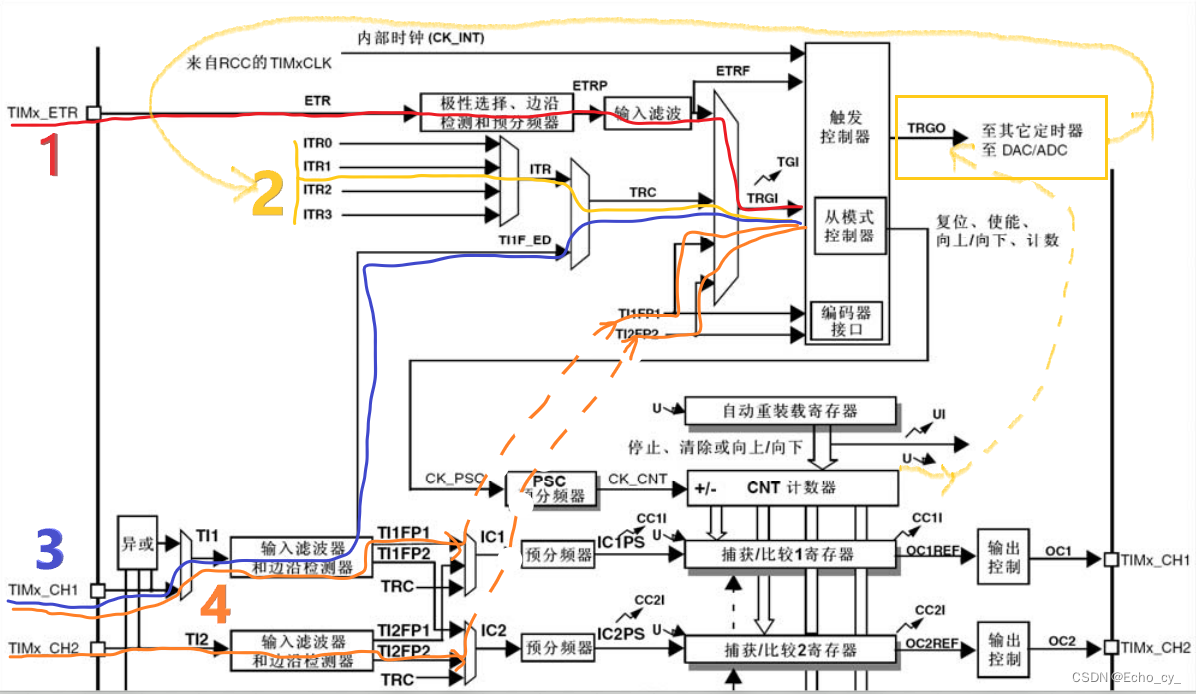

2.2.1 时钟源

外部时钟模式2

外部时钟模式1

1.ETR引脚信号

2.其他定时器信号

3.CH1引脚的边沿信号

4.CH1引脚和CH2引脚信号

2.2.2 控制器

2.2.3 时基单元

2.2.4 输入捕获

2.2.5 捕获/比较寄存器

2.2.6 比较通道

2.3 高级定时器

2.3.1 重复计数器

2.3.2 输出比较模块

2.3.3 刹车输入

三、定时中断基本结构

四、时序图

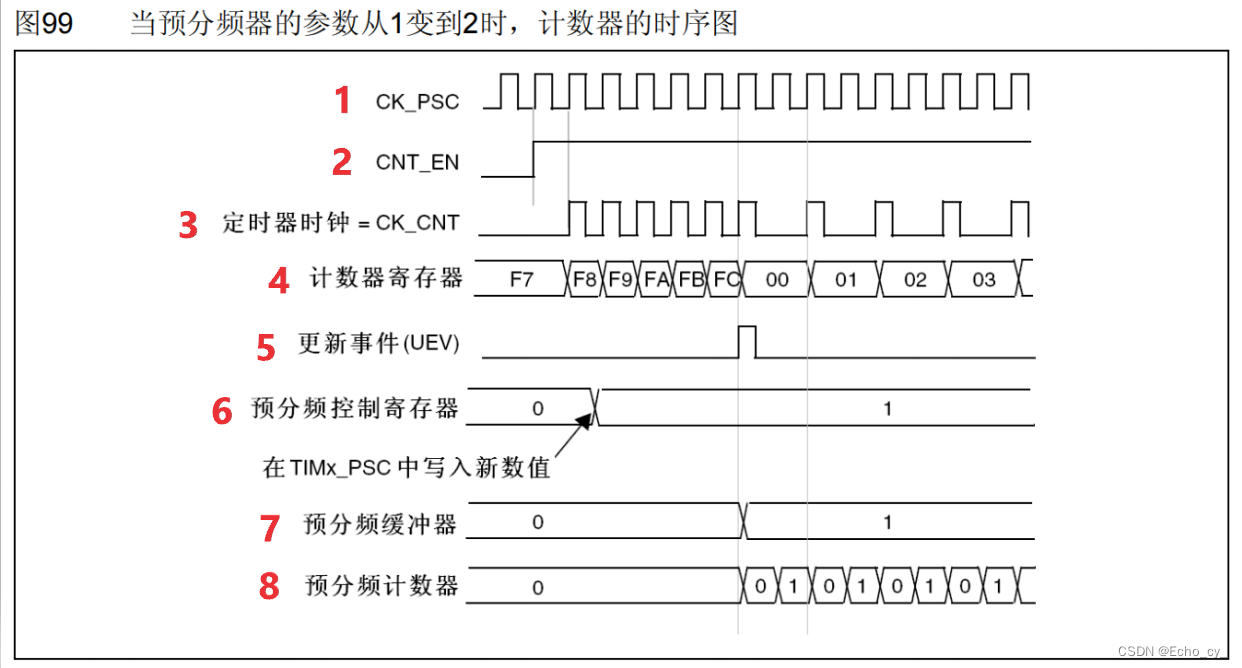

4.1 预分频器时序图

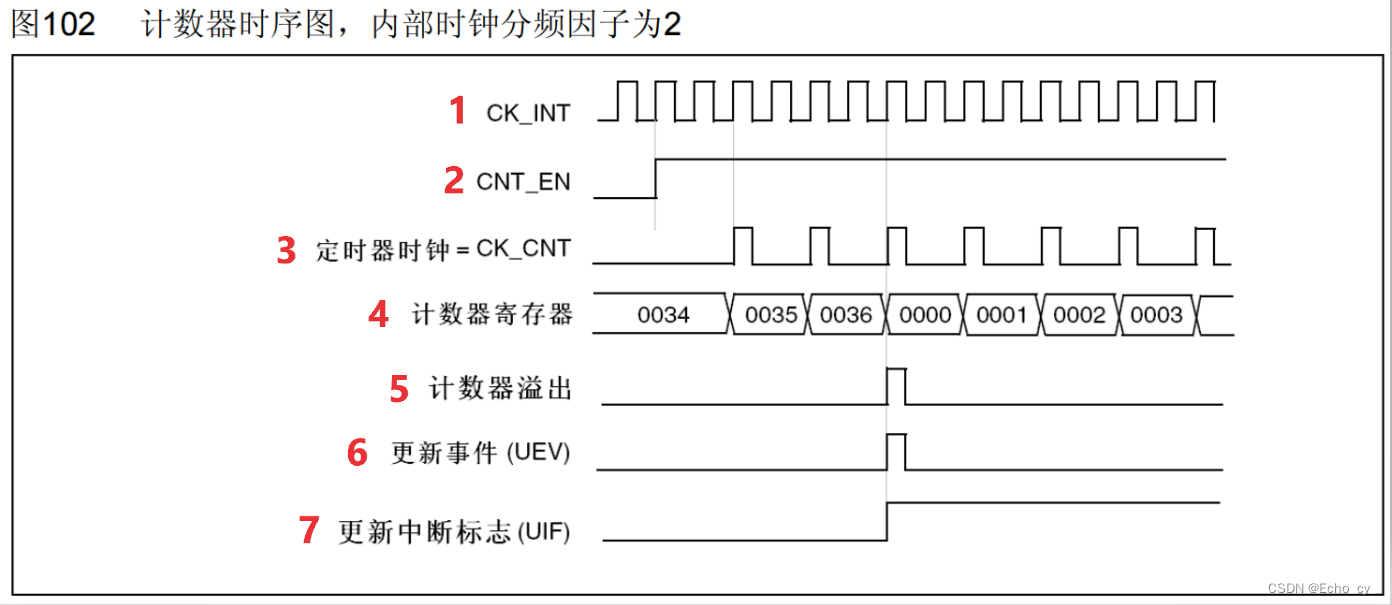

4.2 计数器时序图

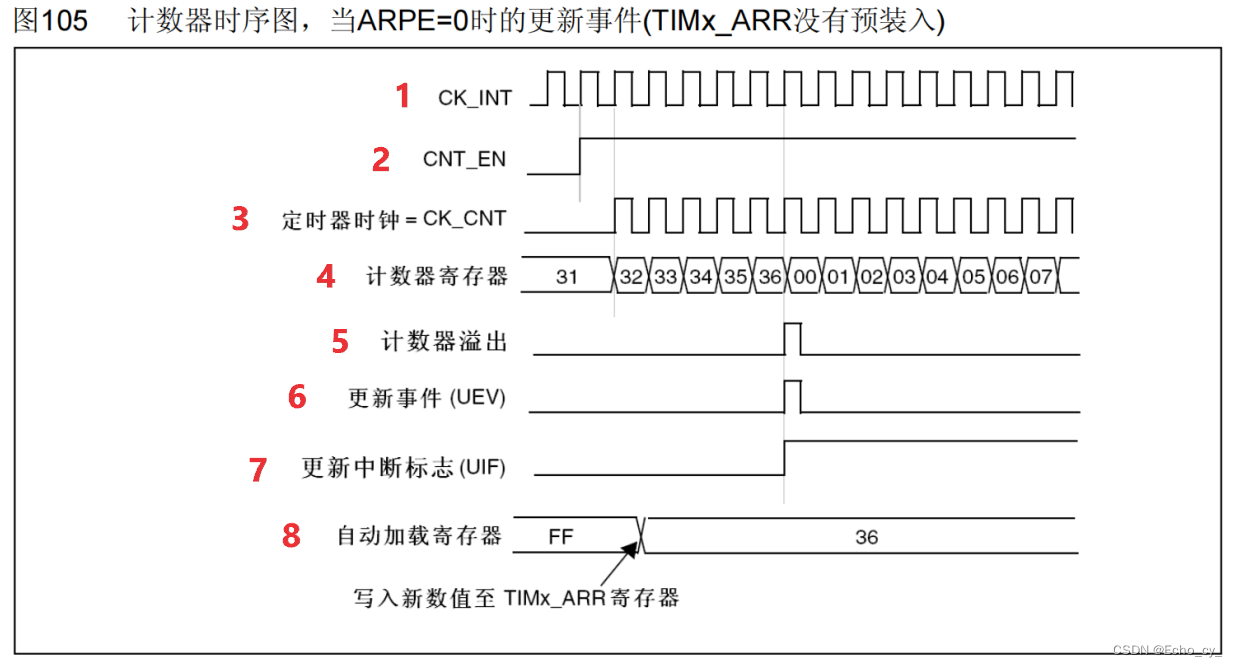

4.3 计数器无预装时序图

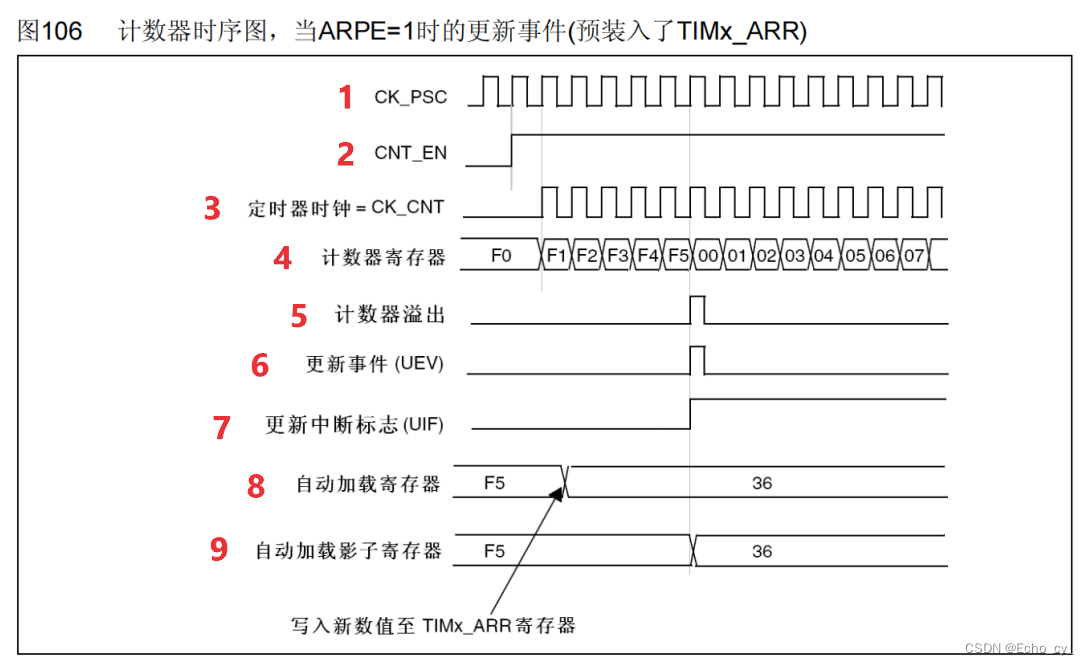

4.4 计数器有预装时序图

总结

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。