基准时钟必须在时钟树的源时钟上定义。例如

,

源时钟可能是设计的输入端口。如果在覆盖传入时钟定义的下游定义基准时钟,

时序分析准确性可能降低

,

因为它会忽略位于重新定义的基准时钟源点之前的插入延迟

,

从而导致无法正确执行偏差计算。之所以不建议这样做,

是因为这可能导致时序分析错误

,

从而导致硬件故障。

,

源时钟可能是设计的输入端口。如果在覆盖传入时钟定义的下游定义基准时钟,

时序分析准确性可能降低

,

因为它会忽略位于重新定义的基准时钟源点之前的插入延迟

,

从而导致无法正确执行偏差计算。之所以不建议这样做,

是因为这可能导致时序分析错误

,

从而导致硬件故障。

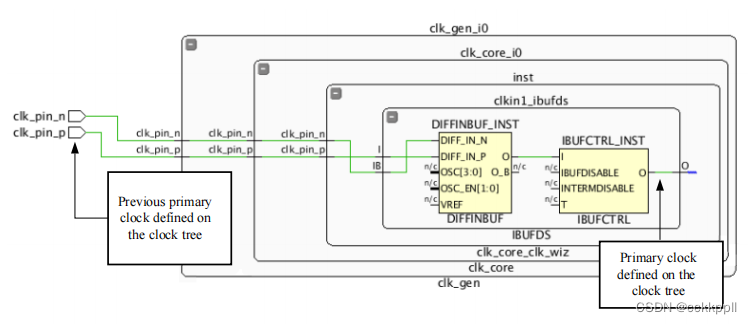

在下图中

,

在顶层端口

clk_pin_p

上已正确定义基准时钟。但

create_clock

约束用于在

IBUFCTRL

输出上重新定义基准时钟。此新时钟将忽略 IBUFCTRL

前的所有延迟。

,

在顶层端口

clk_pin_p

上已正确定义基准时钟。但

create_clock

约束用于在

IBUFCTRL

输出上重新定义基准时钟。此新时钟将忽略 IBUFCTRL

前的所有延迟。

时钟

<clock_name>

与

<clock_name>

之间相互关联

(

一起定时

),

但两者间无公共基准时钟。即使满足时序要求,

设计仍可能失败。要查找这些时钟之间的时序路径

,

请运行以下命令

:

<clock_name>

与

<clock_name>

之间相互关联

(

一起定时

),

但两者间无公共基准时钟。即使满足时序要求,

设计仍可能失败。要查找这些时钟之间的时序路径

,

请运行以下命令

:

<CLOCK_NAME2>]

默认情况下

,

这

2

个报告的时钟被视为相关联时钟

,

并以同步方式进行定时

,

即使这

2

个时钟并非衍生自公共的基准时钟,

且不含有已知相位关系

,

也同样如此。

DRC

警告报告称时序引擎无法保证这些时钟处于同步状态。

,

这

2

个报告的时钟被视为相关联时钟

,

并以同步方式进行定时

,

即使这

2

个时钟并非衍生自公共的基准时钟,

且不含有已知相位关系

,

也同样如此。

DRC

警告报告称时序引擎无法保证这些时钟处于同步状态。

解决办法取决于

2

个时钟域处于异步还是同步状态。对于异步时钟

,

时序例外

(

例如

,

set_max_delay – datapath_only、

set_clock_groups

或

set_false_path

)

应覆盖

2

个域之间的路径。当这

2

个域之间的所有路径都实现例外完全覆盖时,

即可解决

DRC

。

2

个时钟域处于异步还是同步状态。对于异步时钟

,

时序例外

(

例如

,

set_max_delay – datapath_only、

set_clock_groups

或

set_false_path

)

应覆盖

2

个域之间的路径。当这

2

个域之间的所有路径都实现例外完全覆盖时,

即可解决

DRC

。

原文地址:https://blog.csdn.net/cckkppll/article/details/134815961

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:http://www.7code.cn/show_45436.html

如若内容造成侵权/违法违规/事实不符,请联系代码007邮箱:suwngjj01@126.com进行投诉反馈,一经查实,立即删除!

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。