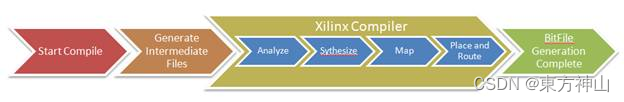

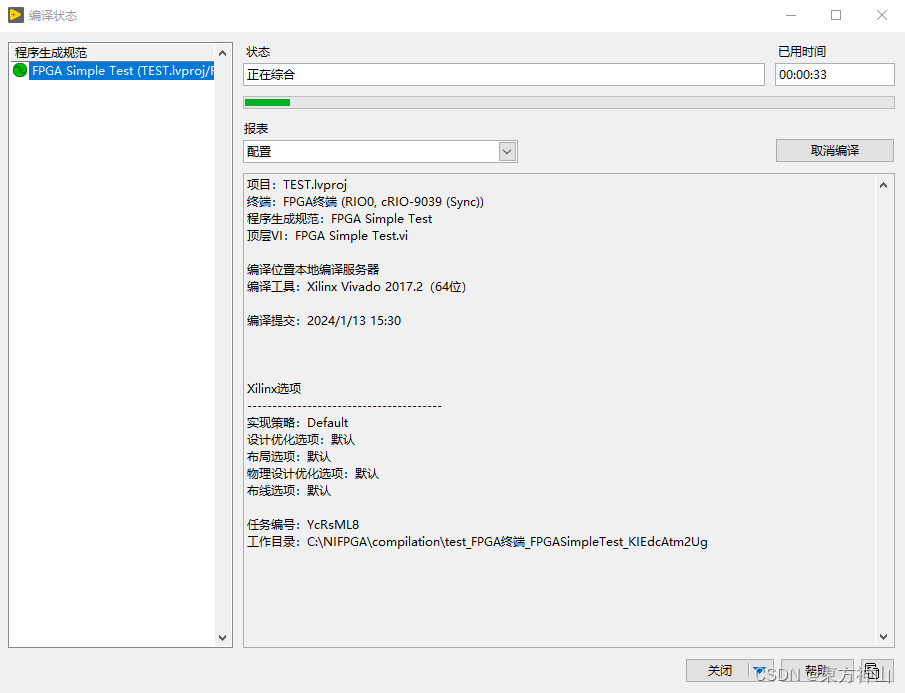

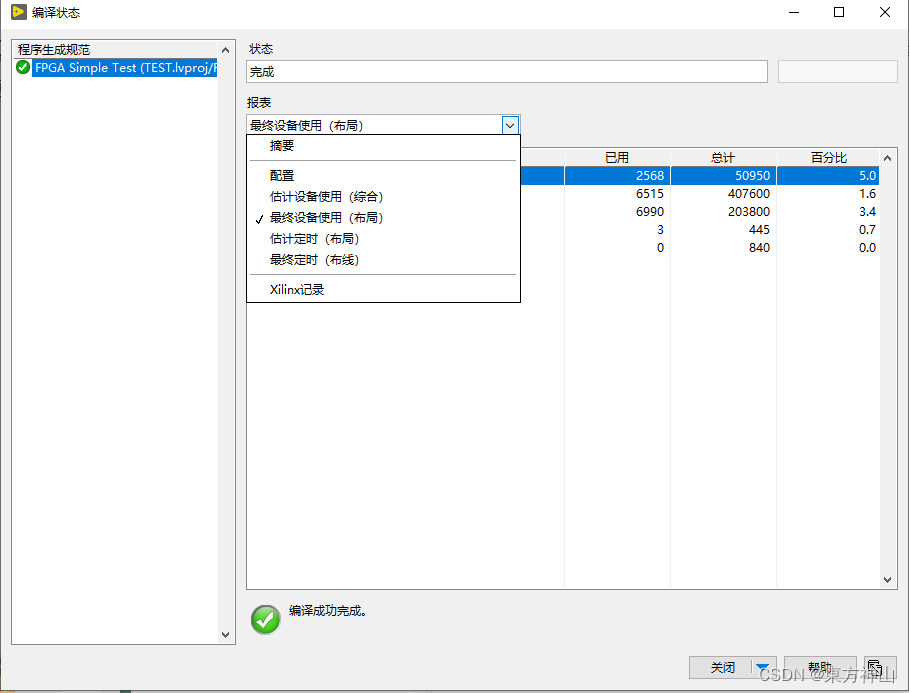

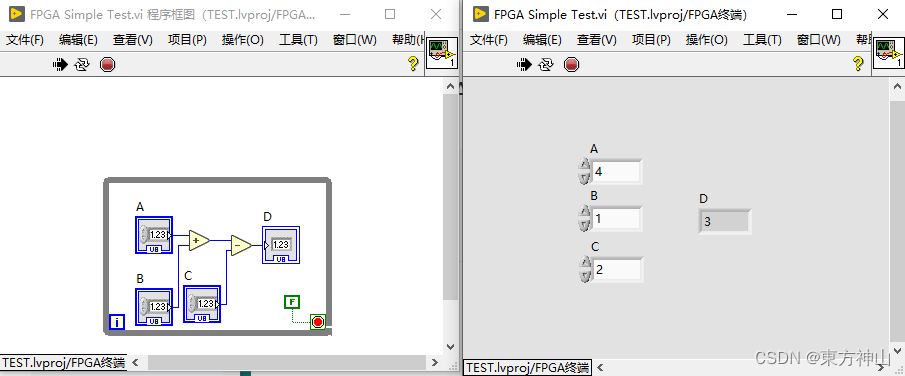

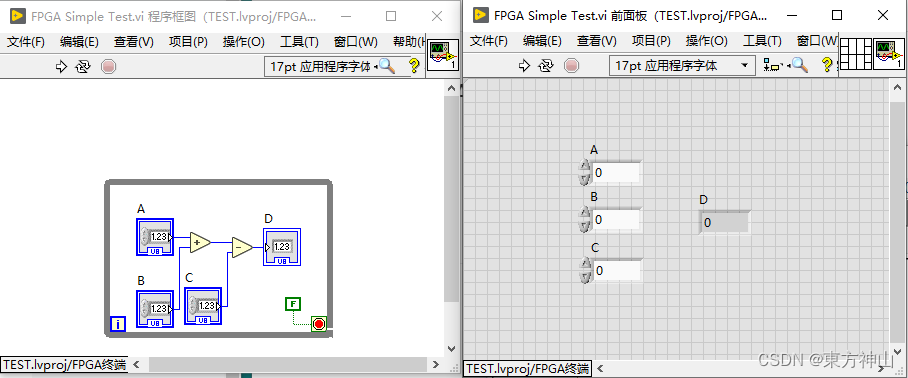

本文介绍: 在LabVIEW FPGA中和rt、PC编程一样使用数据流编程,但是需要注意的是FPGA中有些函数是不可以用的,因为这些函数很占用资源,且FPGA只能同时下载运行一个程序。在此步骤中可能会出现许多错误,导致编译失败。一般编译时间根据代码的大小变化,初学者编译时间大概在5-10分钟,无论使用什么开发软件,FPGA的编译过程都是较久的。7.编译后的FPGA正在运行,可以做一个简单的测试,但是需要注意的是FPGA编程一般是不需要前面板的,同时因为前面板控件占用资源较多,尽量避免在FPGA前面板放太多的控件。

在本文中会进行一个简单的FPGA编程演示,这通常可以验证编译工具链是否正常使用。在LabVIEW FPGA中和rt、PC编程一样使用数据流编程,但是需要注意的是FPGA中有些函数是不可以用的,因为这些函数很占用资源,且FPGA只能同时下载运行一个程序。

1.在FPGA终端下面新建一个VI。

2.打开新创建的VI,随便写一点数学加减法函数用于编译验证编译器功能。

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。