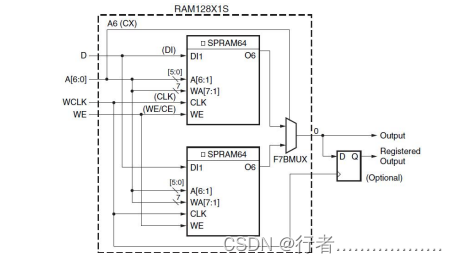

1) 128 X1 Single Port Distributed RAM

下图中可以看出来,通过2个LUT的组合使用可以串联实现更大深度的分布式RAM.下图中出现了F7BMUX的加入, F7BMUX可以用于LUT输出的选通.

原语调用:

RAM128XIS#(INIT(128’h00000000000000000000000000000000) // Initial contents of RAM)RAM128XIS_inst (

.O(O),// 1-bit data output

.A0(A0),

.Al(AI),// Address[1]

.A(A2),

.A3(A3),

.A4(A4),

.A5(A5),//

Α6(A6),// Address[6] input bit

D(D),//1-bit data input

.WCLK(WCLK), //Write clock input

.WE(WE)//Write enable input);

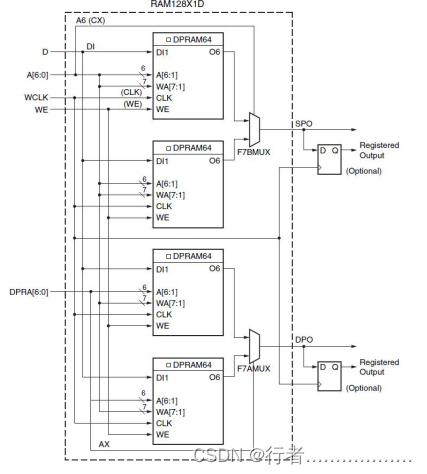

2) 128 X 1 Dual Port Distributed RAM

128×1的双口RAM需要4个LUT实现,正好是一个SLICEM,并且分别使用了F7BMUX和F7AMUX.

原语调用:

RAM128XID#(INIT(128’h000000))

RAM128XID_inst (

.DPO(DPO),// Read port 1-bit output

.SPO(SPO)// Read/write port I-bit output

.A(A).//Read/write port 7-bit address input

.D(D),//RAM data input

.DPRA(DPRA), // Read port 7-bit address input

.WCLK(WCLK),//Write clock input

.WE(WE)// Write enable input);

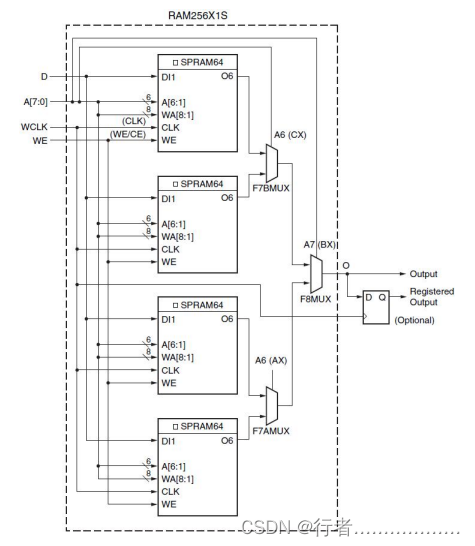

3)256 X1 Single Port Distributed RAM

256×1 的单口 RAM 需要 4个 LUT 实现,也正好是一个 SLICEM,并且分别使用了 F7BMUX 和 F7AMUX以及一个 F8MUX.

原语调用:

RAM256XIS #(INIT(256’h00000))

RAM256XIS_inst (

.O(O)// Read/write port 1-bit output

.A(A),// Read/write port 8-bit address input

.WE(WE)// Write enable input

.WCLK(WCLK), // Write clock input

.D(D)//RAM data input );

原文地址:https://blog.csdn.net/lsh11111/article/details/135759569

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:http://www.7code.cn/show_60755.html

如若内容造成侵权/违法违规/事实不符,请联系代码007邮箱:suwngjj01@126.com进行投诉反馈,一经查实,立即删除!