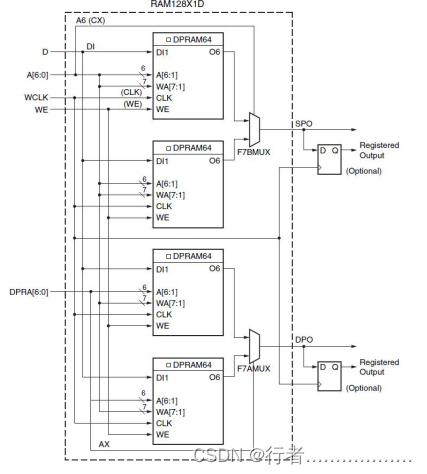

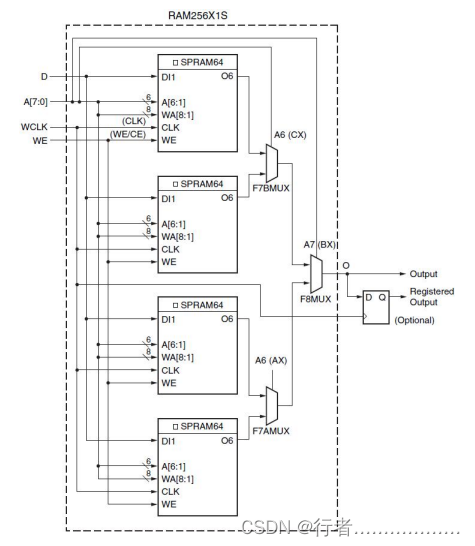

本文介绍: 下图中可以看出来,通过2个LUT的组合使用可以串联实现更大深度的分布式RAM.下图中出现了F7BMUX的加入, F7BMUX可以用于LUT输出的选通.256×1 的单口 RAM 需要 4个 LUT 实现,也正好是一个 SLICEM,并且分别使用了 F7BMUX 和 F7AMUX以及一个 F8MUX.128×1的双口RAM需要4个LUT实现,正好是一个SLICEM,并且分别使用了F7BMUX和F7AMUX.

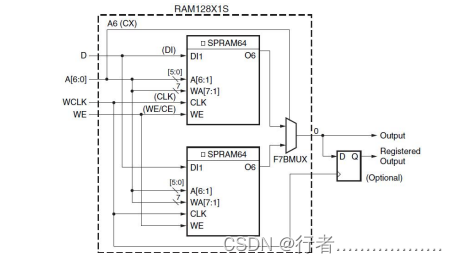

1) 128 X1 Single Port Distributed RAM

下图中可以看出来,通过2个LUT的组合使用可以串联实现更大深度的分布式RAM.下图中出现了F7BMUX的加入, F7BMUX可以用于LUT输出的选通.

原语调用:

RAM128XIS#(INIT(128’h00000000000000000000000000000000) // Initial contents of RAM)RAM128XIS_inst (

.O(O),// 1-bit data output

.A0(A0),

2) 128 X 1 Dual Port Distributed RAM

3)256 X1 Single Port Distributed RAM

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。