CPU 在整个计算机硬件中、技术体系中都算是最最重要的东西了。在 10 月 16 号的时候,Intel 正式发布了第 14 代的酷睿处理器。但很多同学看不懂这种发布会上发布的各种 CPU 参数。

今天借着这个时机,从 CPU 硬件相关的技术细节切入,来深入地讲讲 CPU 的型号规则、代际架构与微架构方面的知识,带领大家更好地认识 CPU。

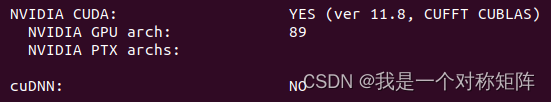

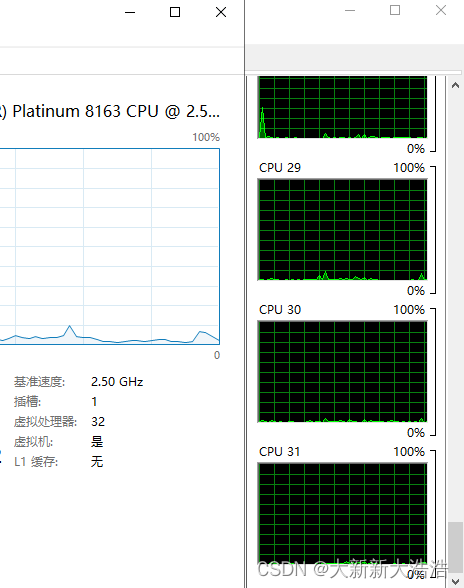

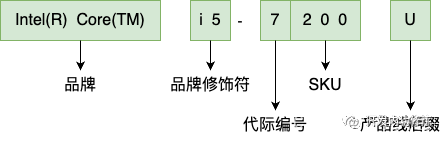

在本文中,我以手头有一台之前用过的 ThinkPad x270 的笔记本电脑举例。在这台电脑中的 CPU 型号是 Intel(R) Core(TM) i5-7200U CPU @ 2.50GHz 2.71 GHz。那么这个型号字符串中都隐含了哪些技术信息呢?接下来,我们以这个型号为切入点,深入地了解个人 PC 电脑中 CPU 硬件相关的技术点。

一、Intel 的 CPU 型号规则

无论是哪家 CPU 厂商,为了更好地管理自己生产的众多型号的产品,也为了能更好地让消费者对自己家的产品快速地了解,都会定义一套产品规则。对于 Intel 来说,它的命令规则大致如下:

二、CPU 的代际

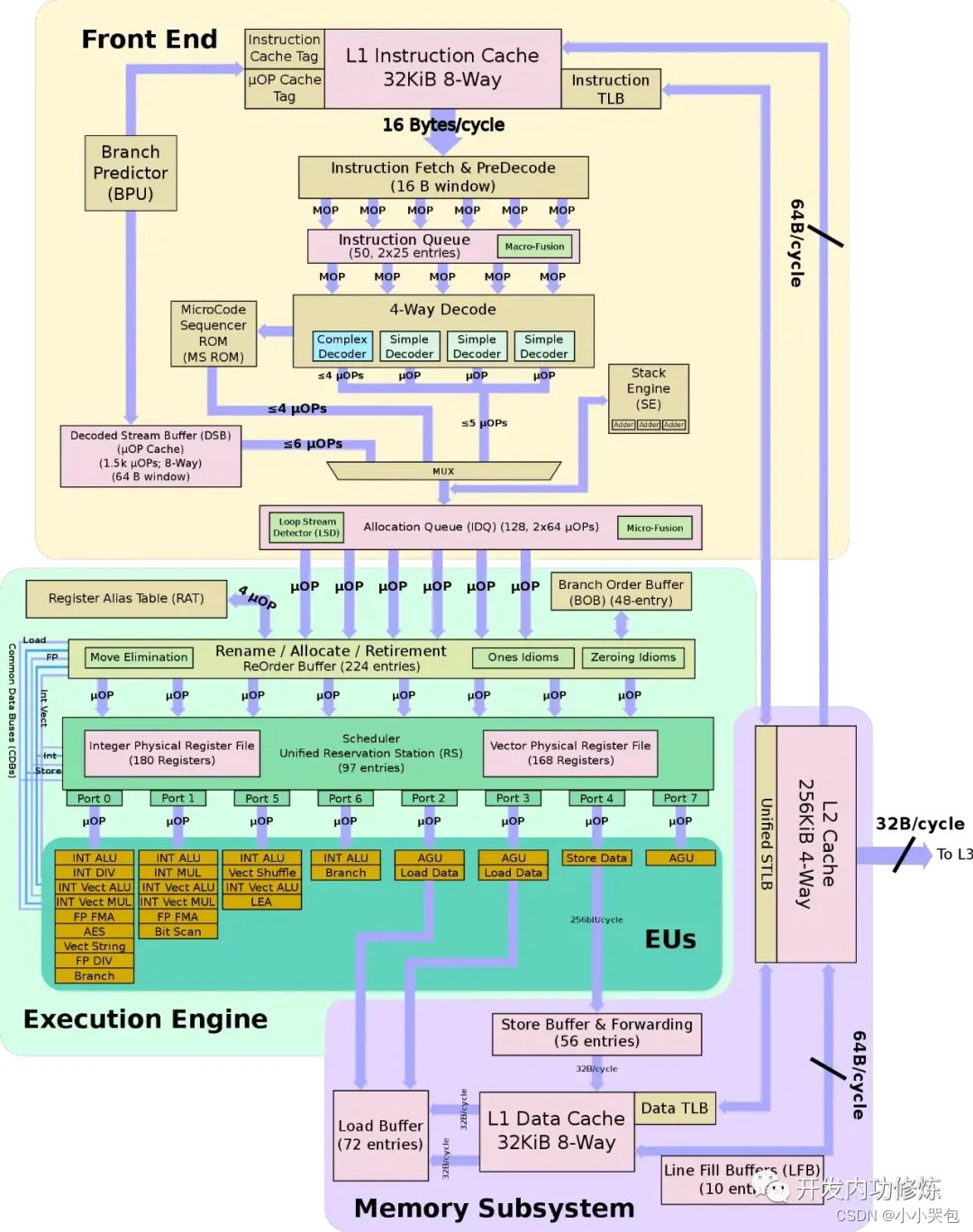

三、物理核微架构设计

总结

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。