Xilinx Zynq-7000系列FPGA实现视频拼接显示,提供两套工程源码和技术支持

1、前言

没玩过视频拼接都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。

目前市面上主流的FPGA视频拼接方案如下:

1:Xilinx的HLS方案,该方案简单,易于实现,但只能用于Xilinx自家的FPGA;

2:非纯Verilog方案,大部分代码使用Verilog实现,但中间的fifo或ram等使用了IP,导致移植性变差,难以在Xilinx、Altera和国产FPGA之间自由移植;

3:纯Verilog方案;

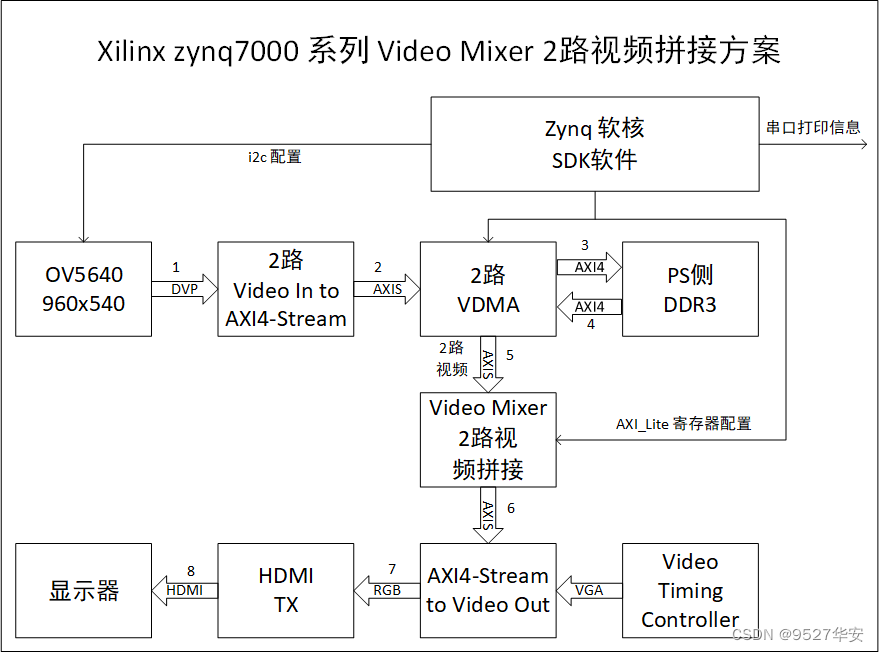

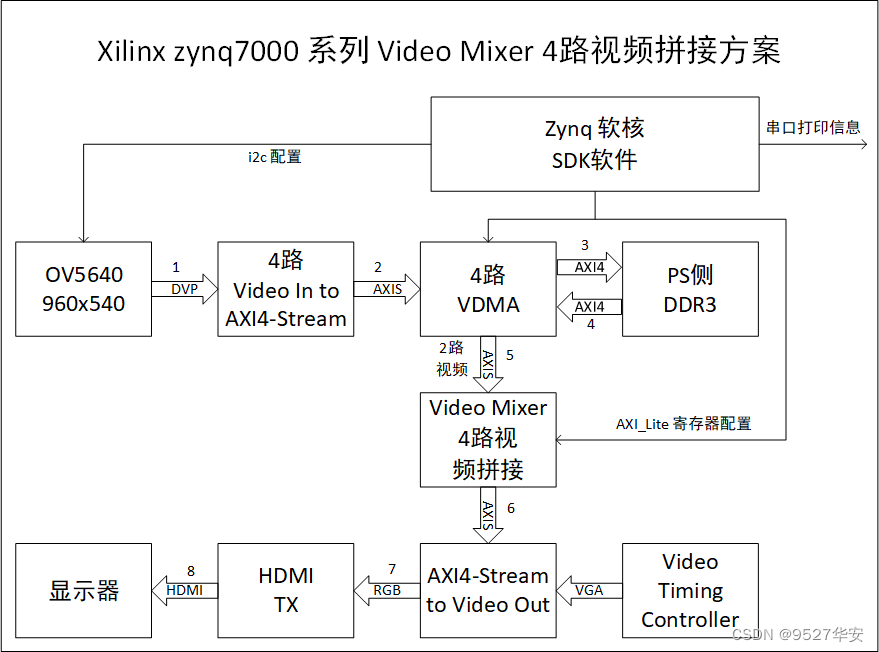

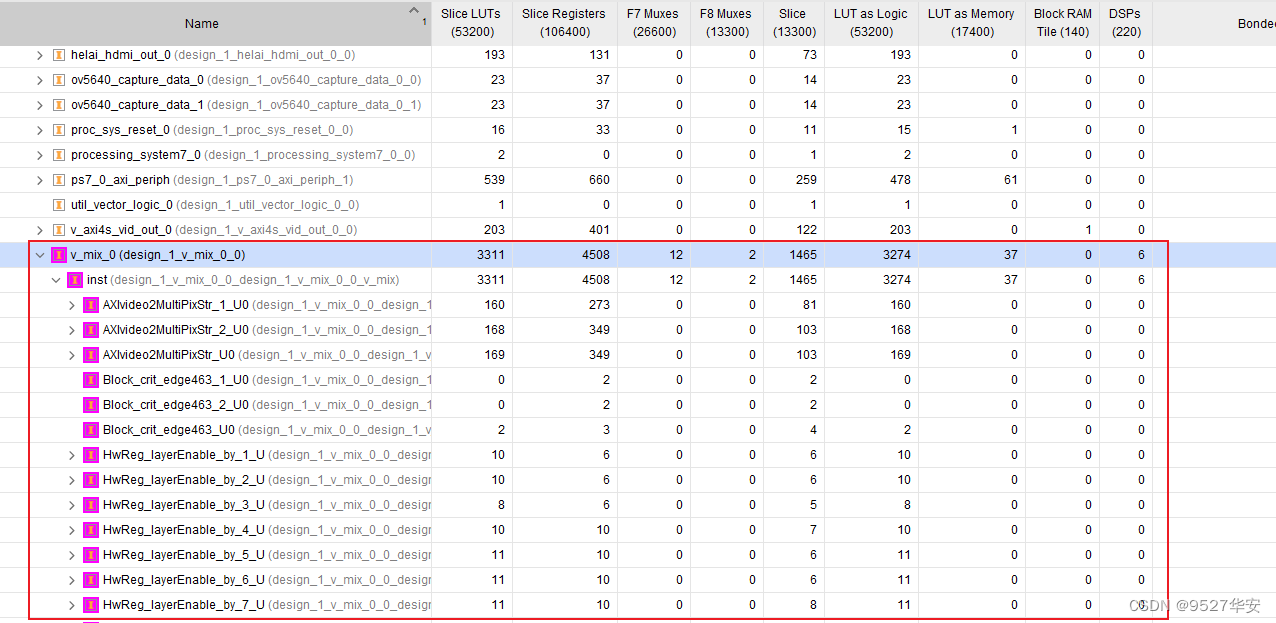

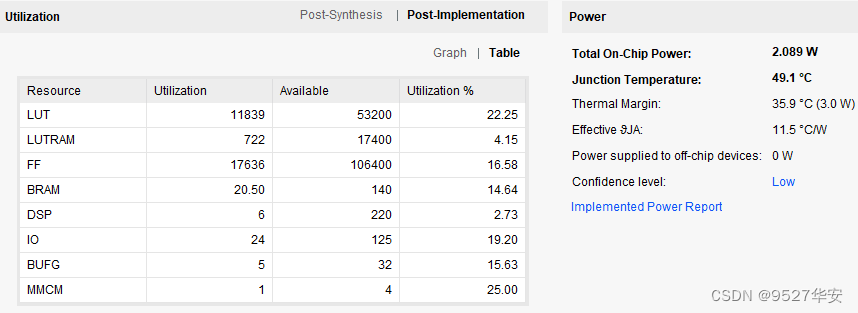

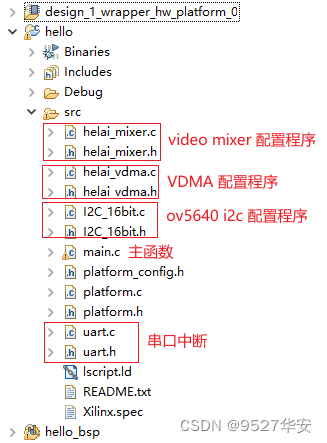

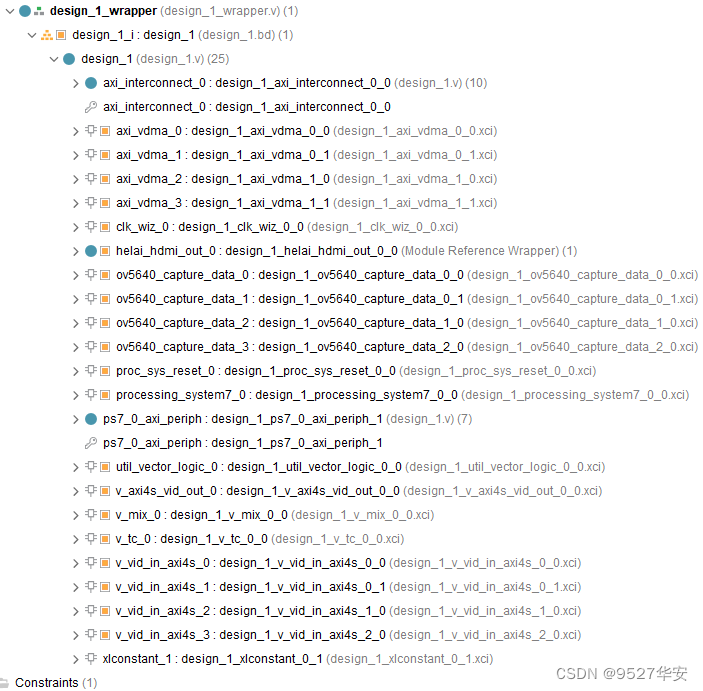

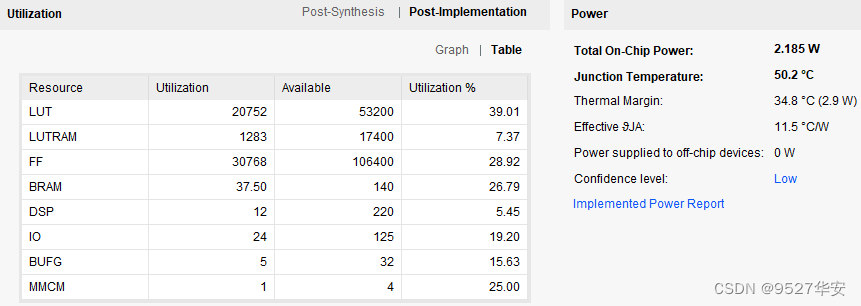

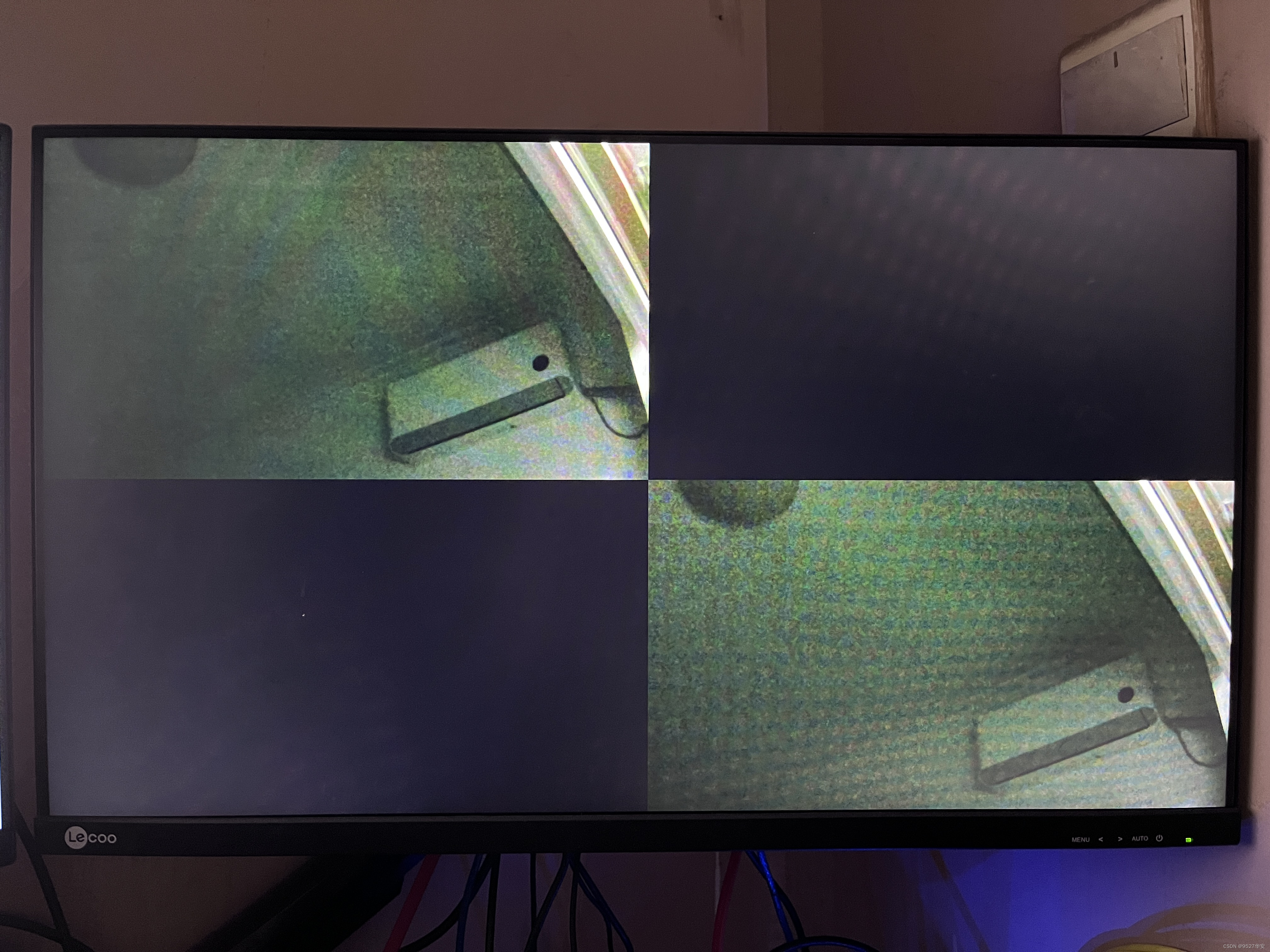

本文使用Xilinx Zynq7000系列FPGA Zynq7020实现HLS图像缩放,输入视频源采用OV5640摄像头模组;FPGA采集OV5640摄像头视频DVP转RGB888,调用Zynq软核的片内i2c控制器将OV5640配置为960×540@30Hz分辨率;工程用一路摄像头数据复制一份来模拟两路摄像头输入;然后调用2个Xilinx官方的Video In to AXI4-Stream IP核将RGB视频流转换为AXI4-Stream视频流;然后调用2个Xilinx官方的VDMA IP将视频做PS侧DDR3的视频缓存操作,VDMA需要Zynq软件配置为三帧缓存,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的Video Mixer IP核做两路视频拼接操作,Video Mixer需要Zynq软件配置为三帧缓存,其本质为通过AXI_Lite 做寄存器配置;然后调用Xilinx官方的Video Timing Controller IP和AXI4-Stream to Video Out IP将AXI4-Stream视频流转换为RGB视频流;然后添加自定义的HDMI发送IP将RGB视频转换为TMDS的差分视频送显示器显示;

提供两套vivado2019.1版本的工程源码和技术支持,两套工程的区别在于拼接的视频路数不同方式不同,详情如下:

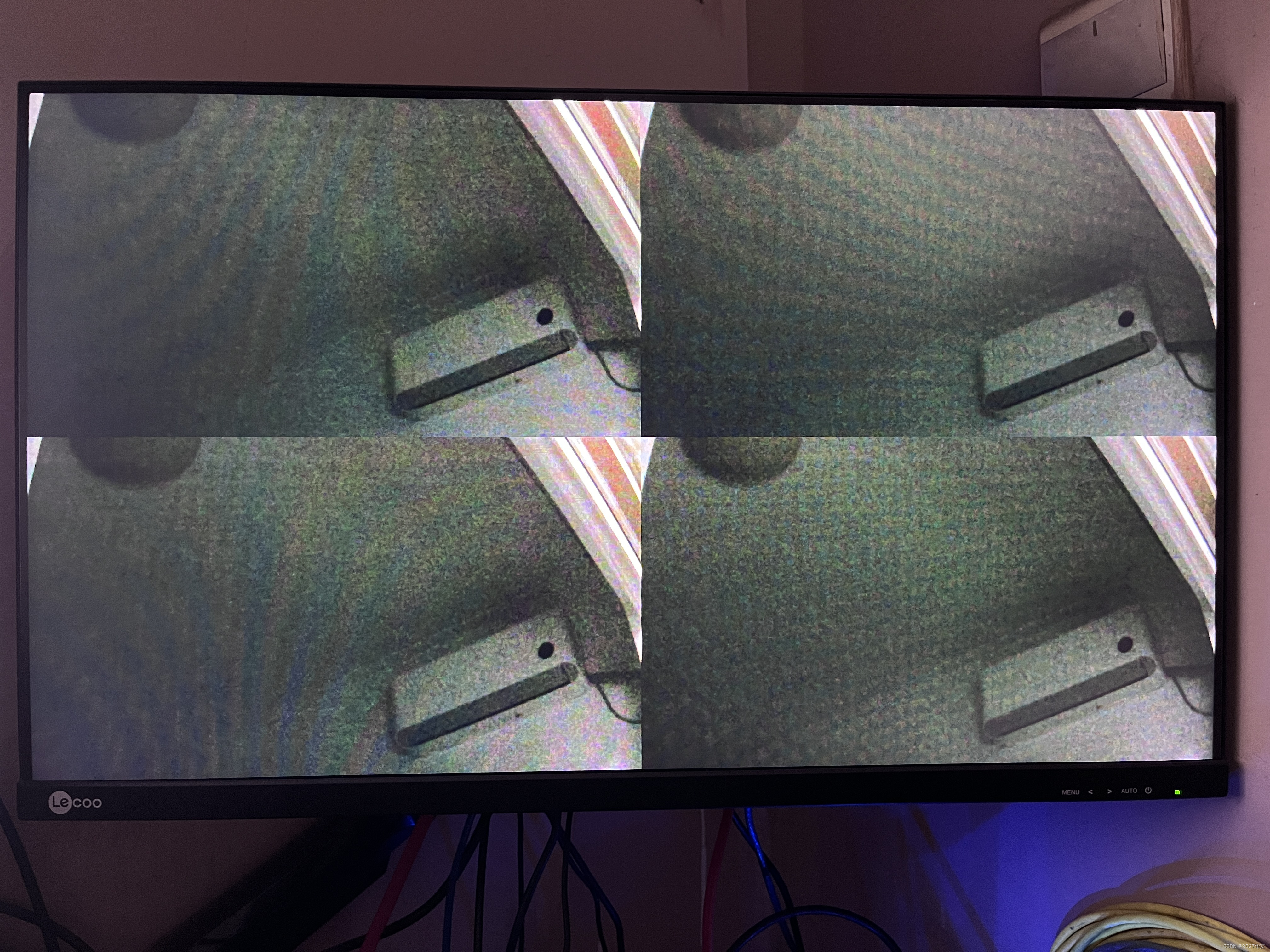

第一套vivado工程源码:输入,OV5640摄像头;2路拼接输出,HDMI显示器;

第二套vivado工程源码:输入,OV5640摄像头;4路拼接输出,HDMI显示器;

Xilinx Zynq-7000系列FPGA实现视频拼接显示的设计方案,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;整个工程调用Zynq软核做IP的配置,Zynq的配置在SDK里以C语言软件代码的形式运行,所以整个工程包括FPGA逻辑设计和SDK软件设计两部分,需要具备FPGA和嵌入式C语言的综合能力,不适合初学者或者小白;