本文介绍: 单片机的扩展结构三种总线的构造方式地址空间分配和外部地址锁存器1.存储器地址空间分配(1)74LS138(2)74LS1392.外部地址锁存器(1)锁存器74LS373静态数据存储器RAM的并行扩展(1)常用的静态RAM (SRAM)芯片(2)外扩数据存储器的读写操作时序1.读片外RAM操作时序2.写片外RAM操作时序(3)AT89S52单片机与RAM的接口设计与软件编程E2PROMA的并行扩展1.读方式2.写方式(1)页写入(2)字节写

三种总线的构造方式

地址空间分配和外部地址锁存器

1.存储器地址空间分配

(1)74LS138

(2)74LS139

2.外部地址锁存器

(1)锁存器74LS373

静态数据存储器RAM的并行扩展

(1)常用的静态RAM (SRAM)芯片

(2)外扩数据存储器的读写操作时序

1.读片外RAM操作时序

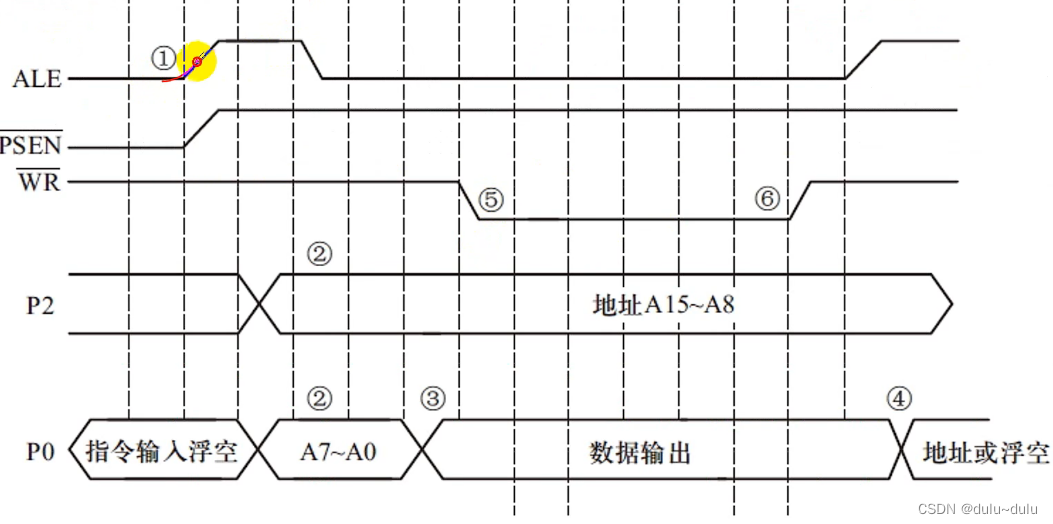

2.写片外RAM操作时序

(3)AT89S52单片机与RAM的接口设计与软件编程

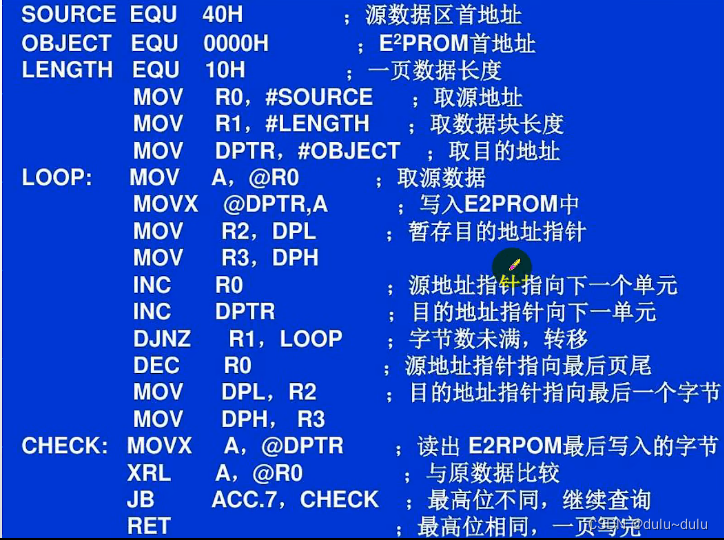

E2PROMA的并行扩展

1.读方式

2.写方式

(1)页写入

(2)字节写入

3.数据查询方式

4.维持方式

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。