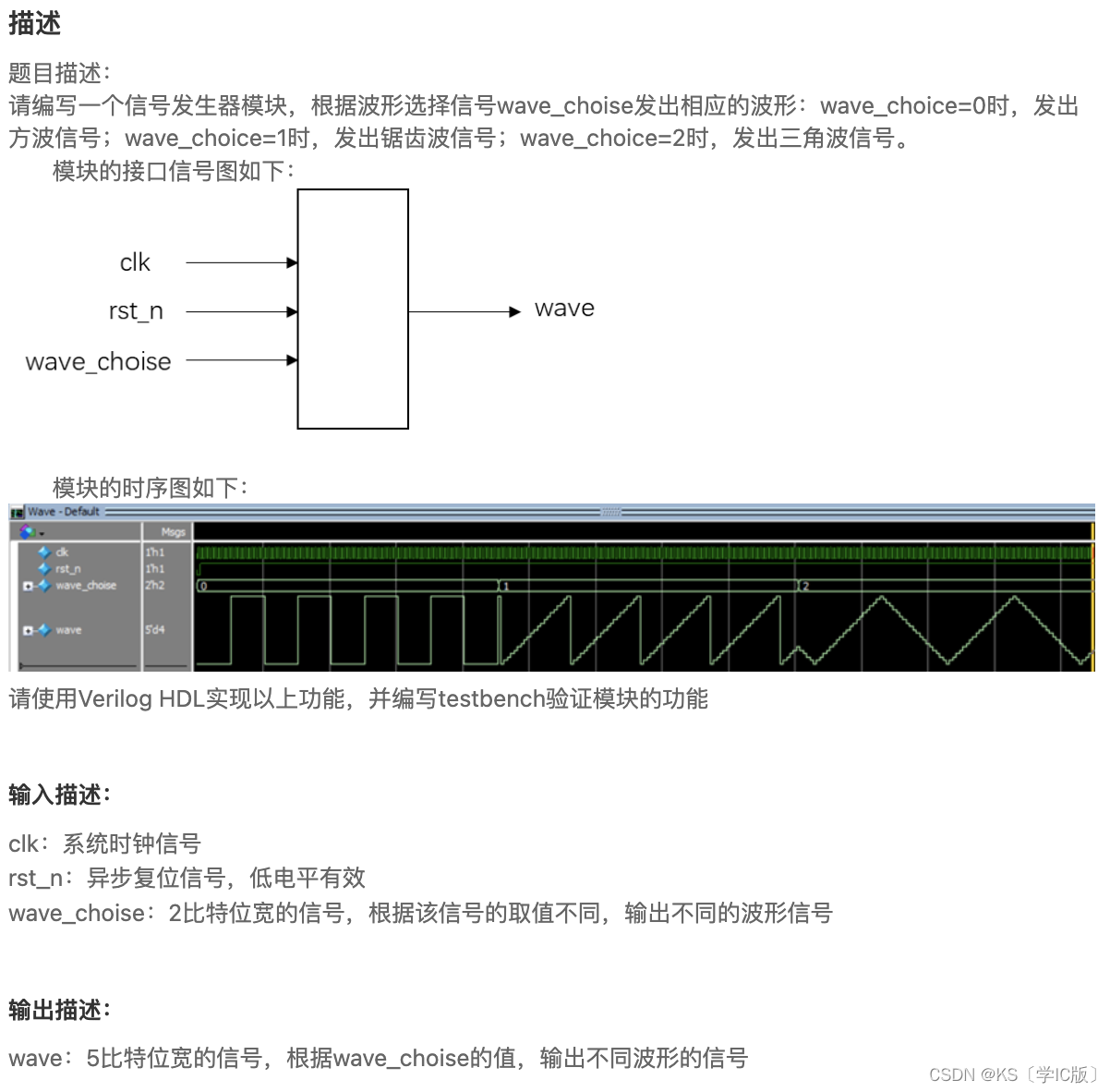

本文介绍: 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网方波的实现,较为简单,只需要设置一个计数器,使输出保持10个时钟为0,跳变为20,再保持10个时钟。依次循环。可以按照如下的过程实现:cnt每个时钟加一,当cnt=19时,将wave的值置为0,同时cnt置为0;当cnt=9时,将wave的值置为20。锯齿波的实现,即输出信号由0每次加一递增到20,然后从20跳变到0。可以按照如下的过程实现:当wave=20,将wave的值置为0,其余时刻,wave加一。

专栏前言

方波的实现,较为简单,只需要设置一个计数器,使输出保持10个时钟为0,跳变为20,再保持10个时钟。依次循环。可以按照如下的过程实现:cnt每个时钟加一,当cnt=19时,将wave的值置为0,同时cnt置为0;当cnt=9时,将wave的值置为20。

锯齿波的实现,即输出信号由0每次加一递增到20,然后从20跳变到0。可以按照如下的过程实现:当wave=20,将wave的值置为0,其余时刻,wave加一。

三角波的实现,类似于锯齿波,但当wave达到20时,不是跳变到0,而是以一为步长递减到0。可以设置一个指示信号up,当up的值是1时,wave每个时钟加一。当up的值为0时,则减一。

`timescale 1ns/1ns

module signal_generator(

input clk,

input rst_n,

input [1:0] wave_choise,

output reg [4:0]wave

);

reg [4:0] cnt ;

reg up ;

always @ (posedge clk or negedge rst_n) begin

if (!rst_n) begin

wave <= 5'd0 ;

cnt <= 5'd0 ;

end

else begin

case (wave_choise)

2'b00 : begin

if (cnt == 5'd19) begin

wave <= 5'd0 ;

cnt <= 5'd0 ;

end

else if (cnt == 5'd9) begin

wave <= 5'd20 ;

cnt <= cnt + 1'd1 ;

end

else begin

wave <= wave ;

cnt <= cnt + 1'd1 ;

end

end

2'b01 : begin

if (wave == 5'd20) wave <= 5'd0 ;

else wave <= wave + 1'd1 ;

end

2'b10 : begin

if (wave == 5'd20) begin

wave <= wave - 1'd1 ;

up <= 1'd0 ;

end

else if (wave == 5'd0) begin

wave <= wave + 1'd1 ;

up <= 1'd1 ;

end

else if (up) wave <= wave + 1'd1 ;

else wave <= wave - 1'd1 ;

end

default :

wave <= 1'b0 ;

endcase

end

end

endmodule原文地址:https://blog.csdn.net/m0_54689021/article/details/134595611

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:http://www.7code.cn/show_19603.html

如若内容造成侵权/违法违规/事实不符,请联系代码007邮箱:suwngjj01@126.com进行投诉反馈,一经查实,立即删除!

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。

![[软件工具]文档页数统计工具软件pdf统计页数word统计页数ppt统计页数图文打印店快速报价工具](https://img-blog.csdnimg.cn/direct/09dfbaff3e9a47a9a551dd65fef5d482.jpeg)