书接上回:

(没看过上面博客的同学,skb是linux对于网络套接字缓冲区的一个虚拟结构体对象)

四、 网络设备驱动实例

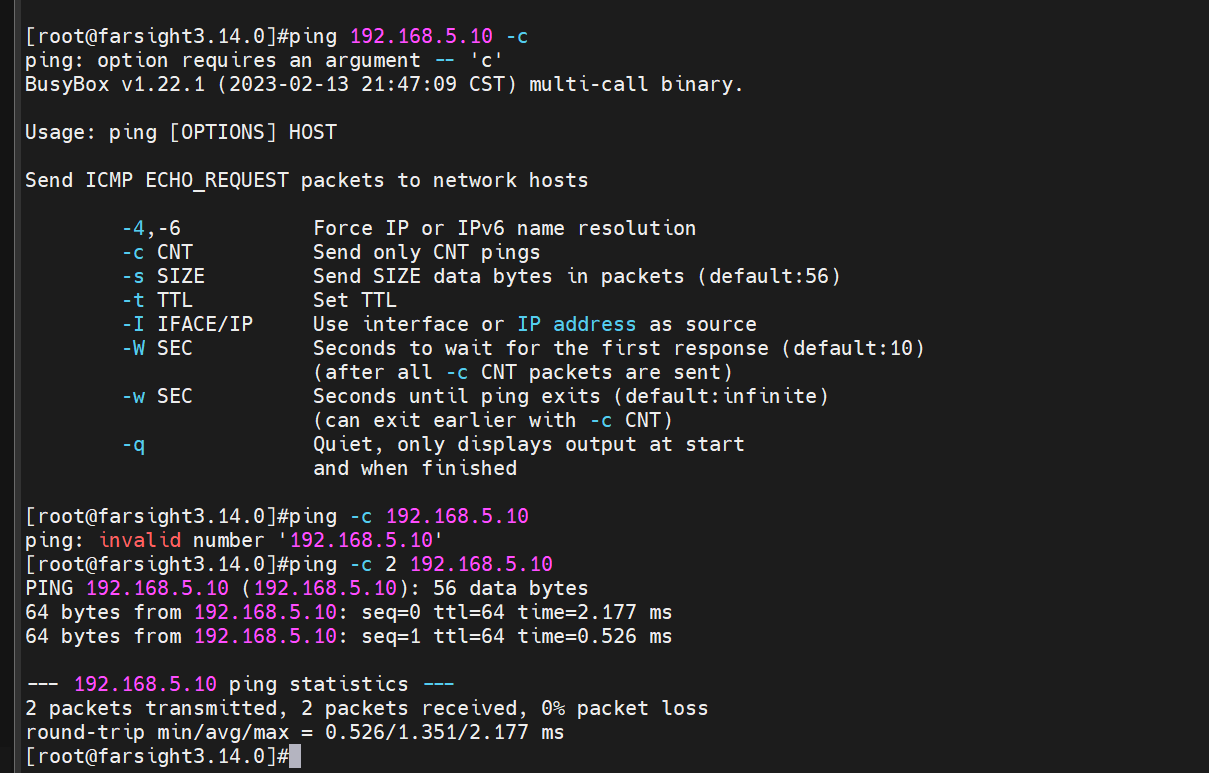

本节实现一个虚拟网络设备的驱动,其目的是使用数据结构和函数来搭建一个网络设备驱动的基本框架。这个虚拟的网络设备是基于内存的,也就是说,要通过网络设备发送的数据包都在驱动内部环回回去,可以实现 ping 命令的测试。但是源IP 地址和目的IP 地址应该不一样,否则上层的内核网络代码将直接使用系统自带的环回网络设备来完成环回。为了欺骗上层的网络模块,让上层感觉数据包被正常发送出去,然后被对端环回回来,在虚拟网络设备驱动的内部,将源地址和目的地址的最后一个字节做了交换,如图所示。

#ifndef __VNET_H__

#define __VNET_H__

#define DEBUG 1

struct vnet_priv {

struct sk_buff *txskb;

int rxlen;

unsigned char rxdata[ETH_DATA_LEN];

};

#endif

在 vnet.h 头文件中定义了一个结构 struct vnet_priv,成员txskb 用于记录发送的skb在发送成功后释放这个 skb。rxdata 则是用于从虚拟网卡中获取的数据包的临时缓冲区rxlen 记录从虚拟网卡中获取的数据包的长度。

#ifndef __VNET_H__

#define __VNET_H__

#define DEBUG 1

struct vnet_priv {

struct sk_buff *txskb;

int rxlen;

unsigned char rxdata[ETH_DATA_LEN];

};

#endif

book@100ask:~/makeru/driver/10_net$ cat vnet.c

#include <linux/init.h>

#include <linux/kernel.h>

#include <linux/module.h>

#include <linux/netdevice.h>

#include <linux/etherdevice.h>

#include <linux/skbuff.h>

#include <linux/ip.h>

#include "vnet.h"

struct net_device *vnet_dev;

static int vnet_open(struct net_device *dev)

{

netif_start_queue(dev);

return 0;

}

static int vnet_stop(struct net_device *dev)

{

netif_stop_queue(dev);

return 0;

}

void vnet_rx(struct net_device *dev)

{

struct sk_buff *skb;

struct vnet_priv *priv = netdev_priv(dev);

skb = dev_alloc_skb(priv->rxlen + 2);

if (IS_ERR(skb)) {

printk(KERN_NOTICE "vnet: low on mem - packet droppedn");

dev->stats.rx_dropped++;

return;

}

skb_reserve(skb, 2);

memcpy(skb_put(skb, priv->rxlen), priv->rxdata, priv->rxlen);

skb->dev = dev;

skb->protocol = eth_type_trans(skb, dev);

skb->ip_summed = CHECKSUM_UNNECESSARY;

dev->stats.rx_packets++;

dev->stats.rx_bytes += priv->rxlen;

netif_rx(skb);

return;

}

static void vnet_rx_int(char *buf, int len, struct net_device *dev)

{

struct vnet_priv *priv;

priv = netdev_priv(dev);

priv->rxlen = len;

memcpy(priv->rxdata, buf, len);

vnet_rx(dev);

return;

}

static void vnet_hw_tx(char *buf, int len, struct net_device *dev)

{

#if DEBUG

int i;

#endif

struct iphdr *ih;

struct net_device *dest;

struct vnet_priv *priv;

u32 *saddr, *daddr;

if (len < sizeof(struct ethhdr) + sizeof(struct iphdr)) {

printk("vnet: Packet too short (%i octets)n", len);

return;

}

#if DEBUG

printk("len is %in", len);

printk("data: ");

for (i = 0; i < len; i++)

printk(" %02x",buf[i] & 0xff);

printk("n");

#endif

ih = (struct iphdr *)(buf + sizeof(struct ethhdr));

saddr = &ih->saddr;

daddr = &ih->daddr;

((u8 *)saddr)[3] = ((u8 *)saddr)[3] ^ ((u8 *)daddr)[3];

((u8 *)daddr)[3] = ((u8 *)saddr)[3] ^ ((u8 *)daddr)[3];

((u8 *)saddr)[3] = ((u8 *)saddr)[3] ^ ((u8 *)daddr)[3];

ih->check = 0;

ih->check = ip_fast_csum((unsigned char *)ih,ih->ihl);

#if DEBUG

printk("len is %in", len);

printk("data: ");

for (i = 0; i < len; i++)

printk(" %02x",buf[i] & 0xff);

printk("nn");

#endif

dest = vnet_dev;

vnet_rx_int(buf, len, dest);

dev->stats.tx_packets++;

dev->stats.tx_bytes += len;

priv = netdev_priv(dev);

dev_kfree_skb(priv->txskb);

}

static netdev_tx_t vnet_tx(struct sk_buff *skb, struct net_device *dev)

{

int len;

char *data, shortpkt[ETH_ZLEN];

struct vnet_priv *priv = netdev_priv(dev);

data = skb->data;

len = skb->len;

if (len < ETH_ZLEN) {

memset(shortpkt, 0, ETH_ZLEN);

memcpy(shortpkt, skb->data, skb->len);

len = ETH_ZLEN;

data = shortpkt;

}

dev->trans_start = jiffies;

priv->txskb = skb;

vnet_hw_tx(data, len, dev);

return 0;

}

static const struct net_device_ops vnet_ops = {

.ndo_open = vnet_open,

.ndo_stop = vnet_stop,

.ndo_start_xmit = vnet_tx,

};

static int __init vnet_init(void)

{

int status;

struct vnet_priv *priv;

vnet_dev = alloc_etherdev(sizeof(struct vnet_priv));

if (IS_ERR(vnet_dev))

return -ENOMEM;

ether_setup(vnet_dev);

vnet_dev->netdev_ops = &vnet_ops;

vnet_dev->flags |= IFF_NOARP;

priv = netdev_priv(vnet_dev);

memset(priv, 0, sizeof(struct vnet_priv));

status = register_netdev(vnet_dev);

if (status) {

free_netdev(vnet_dev);

return status;

}

return 0;

}

static void __exit vnet_exit(void)

{

unregister_netdev(vnet_dev);

free_netdev(vnet_dev);

}

module_init(vnet_init);

module_exit(vnet_exit);

MODULE_LICENSE("GPL");

MODULE_AUTHOR("name <e-mail>");

MODULE_DESCRIPTION("Virtual ethernet driver");

代码第 147 行使用alloc_etherdev 分配了一个struct net_device 结构对象的内存空间和struct vnet_priv 结构对象的内存空间,并按照以太网的相关属性初始化了 struct net_device结构对象。代码第 151行再次调用 ether_setup 初始化了 struct net_device 结构对象。代码第 152 行指定了网络设备的操作方法集合为 vnet_ops,只实现了3 个最基本的函数接口,分别是 ndo_open、ndo_stop 和 ndo_start_xmit,这个在后面会进一步描述。代码第153行给 struct net_device 结构对象的 flags 成员添加了IFF_NOARP 标志,这对这里的虚拟网络设备非常重要,因为没有真实的硬件,所以也没有办法完成 ARP 操作。代码第 154行使用netdev_priv 获取了 struct vnet_priv 结构对象的地址,然后将该结构对象的内存清零。代码第 157 行使用 register_netdev 注册了网络设备。代码第 169 行和第 170 行则是在模块卸载的时候进行注销和释放内存的操作。在 vnet open 函数中使用 netif start_queue 来启动发送队列,从而允许上层发送数据包。而在 vnet_stop 函数中则使用 netif_stop_queue 来停止发送队列。这两个操作完成了最基本的网络设备激活和禁止的操作。

数据包的发送由 vnet_tx 函数来启动,代码第 120 行和第 121 行首先获取了要发送据包的缓冲区起始地址和数据包的长度。如果数据包的长度小于以太网允许的最短数换包长度,那么代码第 122 行和第 127 行则对数据包进行填充,以使数据包满足最短包长度的要求。代码第 128 行记录了数据包发送的时间,代码第 129 行记录了要发送数据的 skb 结构对象指针,方便在发送完成后释放该 skb。最后,代码第 130 行调用 vnet_hw_tx函数来真正发送数据包。

在 vnet_hw_tx 函数中,代码第 74 行至第 77 行依然是对数据包长度的判断。代码第79 行至第 85 行则是为了调试方便将原始数据包的内容打印出来。代码第 87 行至第 92行则是取出源 IP 地址和目的 IP地址,然后将最后一个字节进行交换。代码第 94 行和95 行重新计算校验和。这部分代码和协议相关,不应该出现在网络设备驱动的代码中.但是为了完成环回操作,我们必须要修改地址。代码第 97 行至第 103 行也是调试的目的将修改后的数据包内容打印出来。代码第 105 行指定了应该接收该数据包的网络设备(也就是该虚拟网络设备本身),然后调用 vnet_rx_int 在目的网络设备上模拟产生了一次接收中断,从而来完成数据包的接收,这个将在后面进一步讨论。数据包发送成功后,代码第 108 行和第 109 行完成了发送统计信息的维护,代码第 110 行和第 111 行释放了发送的 skb。

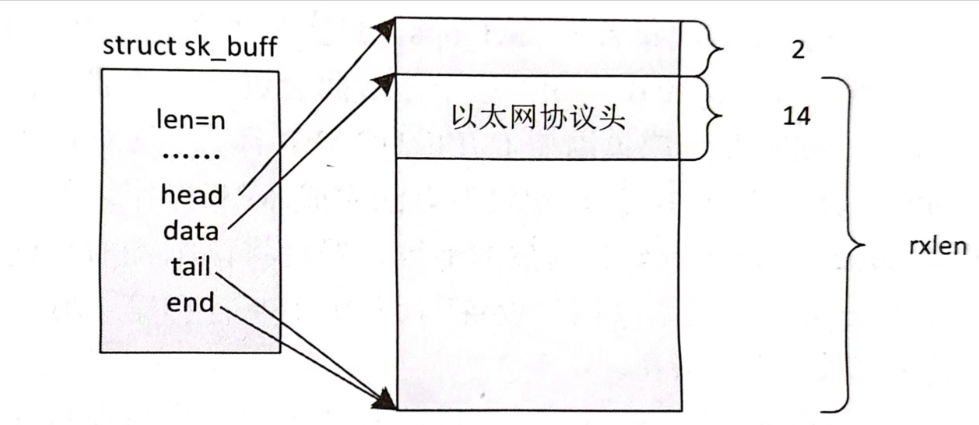

vnet_rx_int 是模拟的数据包接收中断函数,代码第 56 行记录了接收数据包的长度代码第 57 行从网络设备中将数据包复制到了临时的接收缓冲区 rxdata 中,然后调用vnet_rx 做进一步的处理。在 vnet_rx 函数中,代码第 32 行使用 dev_alloc_skb 函数分配一个 skb,虽然是模拟的中断,使用的还是 dev_alloc_skb 函数。skb 的缓冲区长度为rxlen + 2,多分配 2 个字节是为了对齐处理。因为以太网的协议包头为 14 个字节,再多偏移 2 个字节,可以使以太网数据包除去协议头后的净荷数据是 16 字节对齐的,有利充分利用高速缓存来加快对数据的处理过程。代码第 38 行使用 skb_reserve 函数保留个字节正是这个目的。代码第 39 行首先使用 skb_put 函数将 tail 向 end 方向偏移rxlen字节,函数返回的是 put 之前的 tail 指针,然后将数据从临时缓冲区复制到了 skb 中。复制完成后的 skb 示意图如图所示。

代码第 41 行记录接收该数据包的网络设备。代码第 42 行指示接收到的数据包的协议,方便上层对该数据包进行拆包处理。代码第 43 行告诉上层代码不需要做校验和校验,第因为是直接的内存复制。代码第 44 行第 45 行维护收数据包的统计计数,最后使用netif_rx 向上层递交数据包。

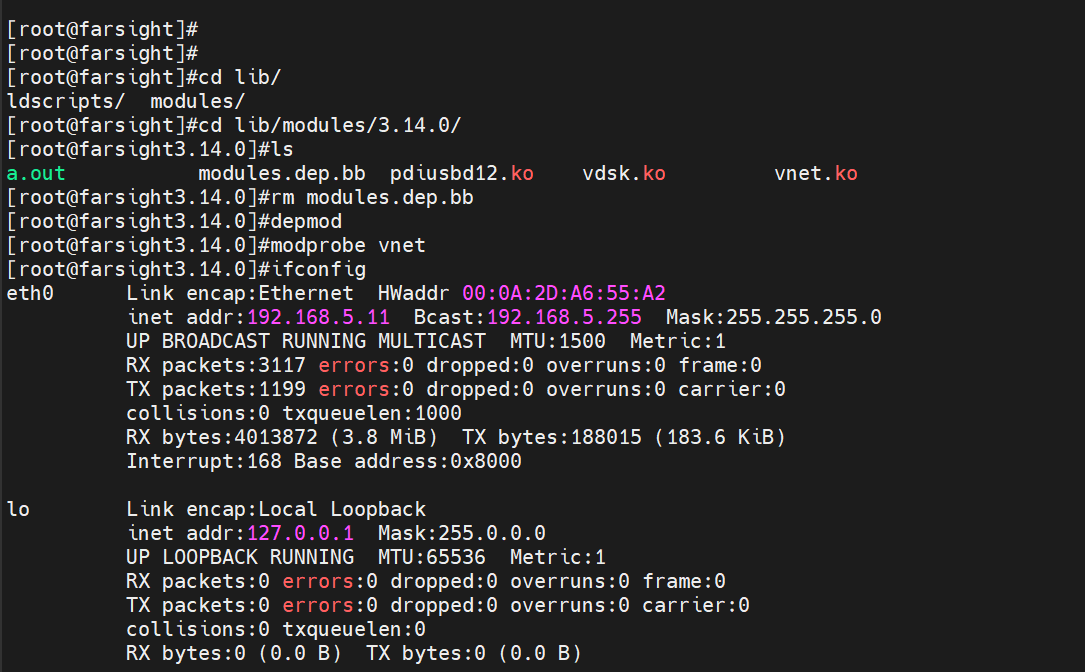

编译和测试的命令如下,使用 dmesg 可以查看调试信息,也可以交叉编译,在目标板上运行。

五、DM9000 网络设备驱动代码分析

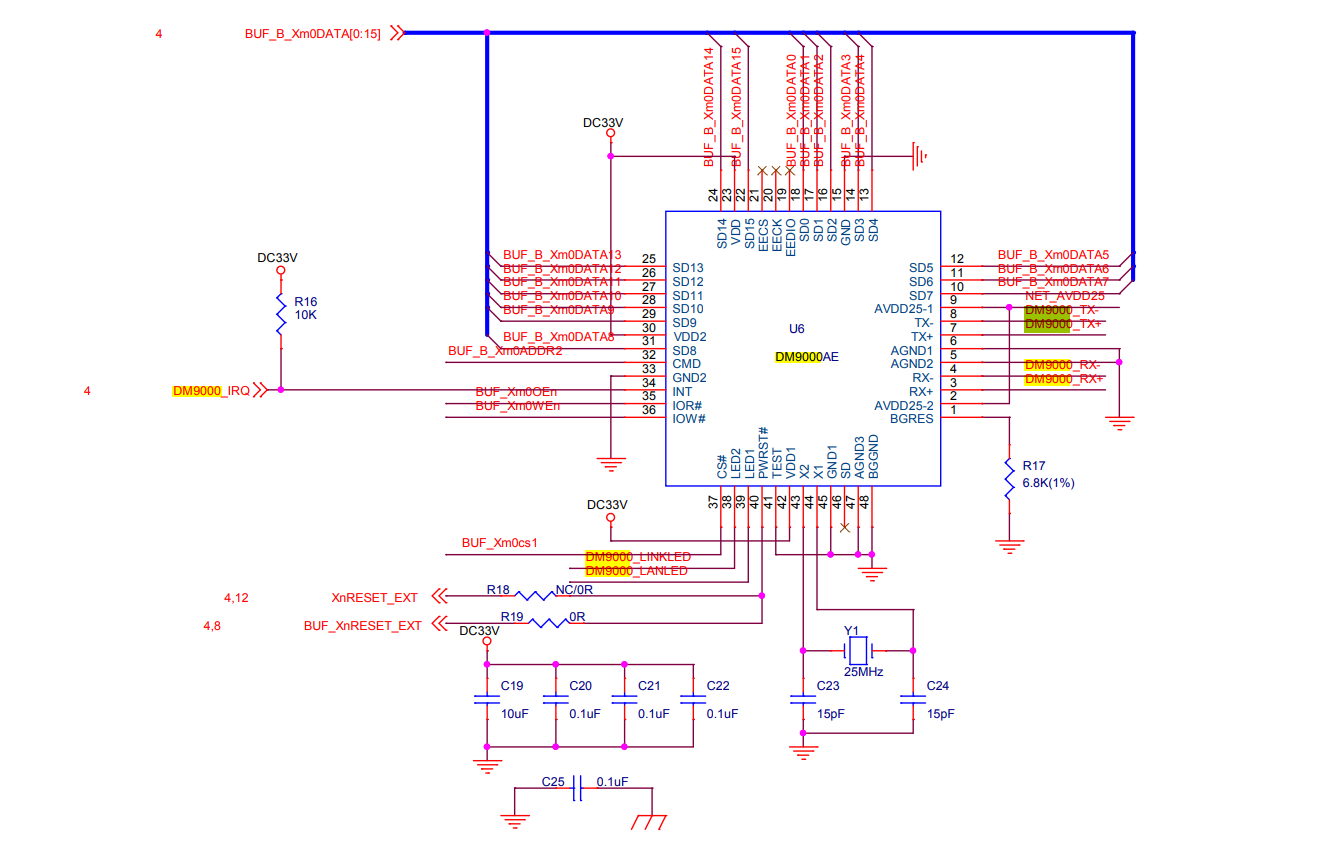

本节将对 DM9000 网络设备驱动做简要的分析,主要是分析其中的核心框架代码,以进一步说明上面的框架是如何应用在真实的网络设备驱动中的。DM9000 在 FS4412 标板上的原理图如图 所示。

DM9000AE 网卡芯片通过存储器总线和 Exynos4412 CPU 芯片相连,片选信号(第37脚)连接到了 Exynos4412的Xm0CSn1 管脚,查看 Exynos4412 的用户手册可知,该片选信号所对应的存储器基地址为 0x05000000.DM9000AE 的 CMD 管脚接在了地址线的ADDR2 上,该管脚决定是访 DM9000AE芯片内部的地址寄存器还是数据寄存器。根据这种接法可知,这两个寄存器的起始地址分别为 0x05000000 和 0x05000004。而数据总线的宽度为 16 位,所以这两个寄存器的结束地址分别为 0x05000001 和 0x05000005。芯片输出了一个中断,连接在了 Exynos4412CPU 芯片的 GPX0 组的 6 号管脚上(对应的中断为 XEINT6),查看 DM9000AE 的芯片手册可知,该管脚为高电平触发方式。

DM9000 网络设备驱动是基于平台驱动的,所以要在设备树文件中编写一个设备树节点,这可以参考内核文档 Documentation/devicetree/bindings/net/davicom-dm9000.txt。根据该文档和上面的硬件信息,得出该设备节点的定义如下。

644 srom-cs1@5000000 {

645 compatible = "simple-bus";

646 #address-cells = <1>;

647 #size-cells = <1>;

648 reg = <0x5000000 0x1000000>;

649 ranges;

650 ethernet@5000000 {

651 compatible = "davicom,dm9000";

652 reg = <0x5000000 0x2 0x5000004 0x2>;

653 interrupt-parent = <&gpx0>;

654 interrupts = <6 4>;

655 davicom,no-eeprom;

656 mac-address = [00 0a 2d a6 55 a2];

657 };

658 };

srom-cs1@5000000 {– 这定义了一个节点,它代表一个内存区域或设备。@5000000表示该设备或内存区域的基地址是0x5000000。compatible = "simple-bus";– 这表示该节点与”simple-bus”兼容,即它是一个简单的总线类型设备。#address-cells = <1>;– 定义地址单元的数量。在这里,它是1,表示子节点的地址是一个单一的数值。#size-cells = <1>;– 定义大小单元的数量。在这里,它也是1,表示子节点的大小是一个单一的数值。reg = <0x5000000 0x1000000>;– 这定义了该设备的物理地址和大小。它的基地址是0x5000000,大小是0x1000000字节。ranges;– 通常用于描述子节点的地址如何映射到父节点的地址空间。在这里,它是空的,可能表示没有映射或默认映射。ethernet@5000000 {– 这定义了一个子节点,代表一个以太网控制器。它的基地址是0x5000000。compatible = "davicom,dm9000";– 表示这个以太网控制器与”davicom,dm9000″兼容。reg = <0x5000000 0x2 0x5000004 0x2>;– 定义该以太网控制器的寄存器布局和大小。interrupt-parent = <&gpx0>;– 表示该设备的中断连接到名为”gpx0″的中断控制器。interrupts = <6 4>;– 这定义了中断号和触发类型。在这里,中断号是6,触发类型是4(通常是边缘触发)。davicom,no-eeprom;– 表示该设备没有EEPROM。mac-address = [00 0a 2d a6 55 a2];– 这是该以太网控制器的MAC地址。};– 结束ethernet@5000000节点的定义。};– 结束srom-cs1@5000000节点的定义。

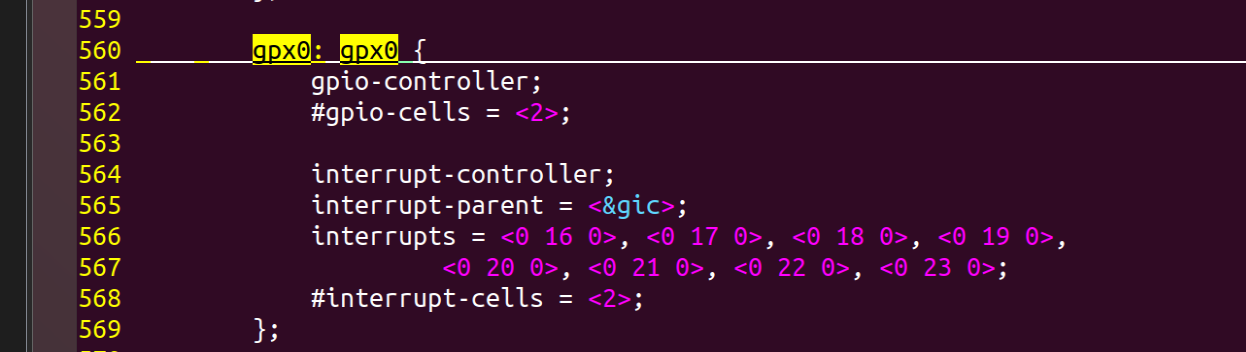

代码首先定义了一个用于地址转换的父节点 srom-esl@50000,该节点的地址范围是0x5000000~0x5FFFFFF,子节点的地址和大小分别用一个cell(一个 32 位的二进制数素表示,1:1 映射。etheret@5000000 是其中的一个子节点,用于描述以太网卡的相关普备信息。其中 compatible 的值为“davicom,dm9000”,和驱动里面的设备列表相符合而reg属性则指定了两个寄存器的起始地址和大小,根据前面关于硬件原理图的分析,不难给出这个属性的值。而 interrupt-parent 则给出了使用中断的父节点,在设备树源文件所包含的一个文件 arch/arm/boot/dts/exynos4×12-pinctrl.dtsi中,定义了如下的一个关于GPX0组管脚的中断节点的定义。

该节点是一个中断控制器,共有 8个中断,分别对应 GPX0的8 个管脚。对 interrupts的解释需要参考 Documentation/devicetree/bindings/arm/gic.txt 文档,其中第一个数字表示中断的类型为 SPI;第二个数字表示 SPI的号,查阅 Exynos4412 的芯片手册可知 EINT6中断对应的 SPI中断号为 22:最后一个数字表示的是中断触发的类型,0为未指定。

ethernet@5000000 节点中的interrupts 属性表示使用了 gpx0 这组中断的以0开始计数的第 6个中断(<0 22 0>这个中断),中断的触发类型为高电平发。该属性值的解读以参考 Documentation/devicetree/bindings/interrupt-controller/interupts.txt 文档中的内容。从硬件原理图分析的结果不难给出该属性的值。

接下来的属性“davicomno-eeprom”表示 DM9000AE 芯片没有外接 EEPROM配置芯片,而 mac–address 属性则指定了以太网卡的 MAC 地址。这些都可以通过查Documentation/devicetree/bindings/net/davicom-dm9000.xt 文档*解释。

DM9000 网络设备驱动的代码的路径为 drivers/net/ethrnet/davicom/dm9000.c,代最后的几行就是支持的设备列表和平台驱动的注册和注销,这和我们之编写的平台整动类似,这里就不再列出代码了。对网络设备的初始化和注册发生在dm9000_probe 涵数中,接下来做简要的分析。

/*

* Davicom DM9000 Fast Ethernet driver for Linux.

* Copyright (C) 1997 Sten Wang

*

* This program is free software; you can redistribute it and/or

* modify it under the terms of the GNU General Public License

* as published by the Free Software Foundation; either version 2

* of the License, or (at your option) any later version.

*

* This program is distributed in the hope that it will be useful,

* but WITHOUT ANY WARRANTY; without even the implied warranty of

* MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE. See the

* GNU General Public License for more details.

*

* (C) Copyright 1997-1998 DAVICOM Semiconductor,Inc. All Rights Reserved.

*

* Additional updates, Copyright:

* Ben Dooks <ben@simtec.co.uk>

* Sascha Hauer <s.hauer@pengutronix.de>

*/

#include <linux/module.h>

#include <linux/ioport.h>

#include <linux/netdevice.h>

#include <linux/etherdevice.h>

#include <linux/interrupt.h>

#include <linux/skbuff.h>

#include <linux/spinlock.h>

#include <linux/crc32.h>

#include <linux/mii.h>

#include <linux/of.h>

#include <linux/of_net.h>

#include <linux/ethtool.h>

#include <linux/dm9000.h>

#include <linux/delay.h>

#include <linux/platform_device.h>

#include <linux/irq.h>

#include <linux/slab.h>

#include <asm/delay.h>

#include <asm/irq.h>

#include <asm/io.h>

#include "dm9000.h"

/* Board/System/Debug information/definition ---------------- */

#define DM9000_PHY 0x40 /* PHY address 0x01 */

#define CARDNAME "dm9000"

#define DRV_VERSION "1.31"

/*

* Transmit timeout, default 5 seconds.

*/

static int watchdog = 5000;

module_param(watchdog, int, 0400);

MODULE_PARM_DESC(watchdog, "transmit timeout in milliseconds");

/*

* Debug messages level

*/

static int debug;

module_param(debug, int, 0644);

MODULE_PARM_DESC(debug, "dm9000 debug level (0-4)");

/* DM9000 register address locking.

*

* The DM9000 uses an address register to control where data written

* to the data register goes. This means that the address register

* must be preserved over interrupts or similar calls.

*

* During interrupt and other critical calls, a spinlock is used to

* protect the system, but the calls themselves save the address

* in the address register in case they are interrupting another

* access to the device.

*

* For general accesses a lock is provided so that calls which are

* allowed to sleep are serialised so that the address register does

* not need to be saved. This lock also serves to serialise access

* to the EEPROM and PHY access registers which are shared between

* these two devices.

*/

/* The driver supports the original DM9000E, and now the two newer

* devices, DM9000A and DM9000B.

*/

enum dm9000_type {

TYPE_DM9000E, /* original DM9000 */

TYPE_DM9000A,

TYPE_DM9000B

};

/* Structure/enum declaration ------------------------------- */

typedef struct board_info {

void __iomem *io_addr; /* Register I/O base address */

void __iomem *io_data; /* Data I/O address */

u16 irq; /* IRQ */

u16 tx_pkt_cnt;

u16 queue_pkt_len;

u16 queue_start_addr;

u16 queue_ip_summed;

u16 dbug_cnt;

u8 io_mode; /* 0:word, 2:byte */

u8 phy_addr;

u8 imr_all;

unsigned int flags;

unsigned int in_suspend:1;

unsigned int wake_supported:1;

enum dm9000_type type;

void (*inblk)(void __iomem *port, void *data, int length);

void (*outblk)(void __iomem *port, void *data, int length);

void (*dumpblk)(void __iomem *port, int length);

struct device *dev; /* parent device */

struct resource *addr_res; /* resources found */

struct resource *data_res;

struct resource *addr_req; /* resources requested */

struct resource *data_req;

struct resource *irq_res;

int irq_wake;

struct mutex addr_lock; /* phy and eeprom access lock */

struct delayed_work phy_poll;

struct net_device *ndev;

spinlock_t lock;

struct mii_if_info mii;

u32 msg_enable;

u32 wake_state;

int ip_summed;

} board_info_t;

/* debug code */

#define dm9000_dbg(db, lev, msg...) do {

if ((lev) < debug) {

dev_dbg(db->dev, msg);

}

} while (0)

static inline board_info_t *to_dm9000_board(struct net_device *dev)

{

return netdev_priv(dev);

}

/* DM9000 network board routine ---------------------------- */

/*

* Read a byte from I/O port

*/

static u8

ior(board_info_t *db, int reg)

{

writeb(reg, db->io_addr);

return readb(db->io_data);

}

/*

* Write a byte to I/O port

*/

static void

iow(board_info_t *db, int reg, int value)

{

writeb(reg, db->io_addr);

writeb(value, db->io_data);

}

static void

dm9000_reset(board_info_t *db)

{

dev_dbg(db->dev, "resetting devicen");

/* Reset DM9000, see DM9000 Application Notes V1.22 Jun 11, 2004 page 29

* The essential point is that we have to do a double reset, and the

* instruction is to set LBK into MAC internal loopback mode.

*/

iow(db, DM9000_NCR, 0x03);

udelay(100); /* Application note says at least 20 us */

if (ior(db, DM9000_NCR) & 1)

dev_err(db->dev, "dm9000 did not respond to first resetn");

iow(db, DM9000_NCR, 0);

iow(db, DM9000_NCR, 0x03);

udelay(100);

if (ior(db, DM9000_NCR) & 1)

dev_err(db->dev, "dm9000 did not respond to second resetn");

}

/* routines for sending block to chip */

static void dm9000_outblk_8bit(void __iomem *reg, void *data, int count)

{

iowrite8_rep(reg, data, count);

}

static void dm9000_outblk_16bit(void __iomem *reg, void *data, int count)

{

iowrite16_rep(reg, data, (count+1) >> 1);

}

static void dm9000_outblk_32bit(void __iomem *reg, void *data, int count)

{

iowrite32_rep(reg, data, (count+3) >> 2);

}

/* input block from chip to memory */

static void dm9000_inblk_8bit(void __iomem *reg, void *data, int count)

{

ioread8_rep(reg, data, count);

}

static void dm9000_inblk_16bit(void __iomem *reg, void *data, int count)

{

ioread16_rep(reg, data, (count+1) >> 1);

}

static void dm9000_inblk_32bit(void __iomem *reg, void *data, int count)

{

ioread32_rep(reg, data, (count+3) >> 2);

}

/* dump block from chip to null */

static void dm9000_dumpblk_8bit(void __iomem *reg, int count)

{

int i;

int tmp;

for (i = 0; i < count; i++)

tmp = readb(reg);

}

static void dm9000_dumpblk_16bit(void __iomem *reg, int count)

{

int i;

int tmp;

count = (count + 1) >> 1;

for (i = 0; i < count; i++)

tmp = readw(reg);

}

static void dm9000_dumpblk_32bit(void __iomem *reg, int count)

{

int i;

int tmp;

count = (count + 3) >> 2;

for (i = 0; i < count; i++)

tmp = readl(reg);

}

/*

* Sleep, either by using msleep() or if we are suspending, then

* use mdelay() to sleep.

*/

static void dm9000_msleep(board_info_t *db, unsigned int ms)

{

if (db->in_suspend)

mdelay(ms);

else

msleep(ms);

}

/* Read a word from phyxcer */

static int

dm9000_phy_read(struct net_device *dev, int phy_reg_unused, int reg)

{

board_info_t *db = netdev_priv(dev);

unsigned long flags;

unsigned int reg_save;

int ret;

mutex_lock(&db->addr_lock);

spin_lock_irqsave(&db->lock, flags);

/* Save previous register address */

reg_save = readb(db->io_addr);

/* Fill the phyxcer register into REG_0C */

iow(db, DM9000_EPAR, DM9000_PHY | reg);

/* Issue phyxcer read command */

iow(db, DM9000_EPCR, EPCR_ERPRR | EPCR_EPOS);

writeb(reg_save, db->io_addr);

spin_unlock_irqrestore(&db->lock, flags);

dm9000_msleep(db, 1); /* Wait read complete */

spin_lock_irqsave(&db->lock, flags);

reg_save = readb(db->io_addr);

iow(db, DM9000_EPCR, 0x0); /* Clear phyxcer read command */

/* The read data keeps on REG_0D & REG_0E */

ret = (ior(db, DM9000_EPDRH) << 8) | ior(db, DM9000_EPDRL);

/* restore the previous address */

writeb(reg_save, db->io_addr);

spin_unlock_irqrestore(&db->lock, flags);

mutex_unlock(&db->addr_lock);

dm9000_dbg(db, 5, "phy_read[%02x] -> %04xn", reg, ret);

return ret;

}

/* Write a word to phyxcer */

static void

dm9000_phy_write(struct net_device *dev,

int phyaddr_unused, int reg, int value)

{

board_info_t *db = netdev_priv(dev);

unsigned long flags;

unsigned long reg_save;

dm9000_dbg(db, 5, "phy_write[%02x] = %04xn", reg, value);

mutex_lock(&db->addr_lock);

spin_lock_irqsave(&db->lock, flags);

/* Save previous register address */

reg_save = readb(db->io_addr);

/* Fill the phyxcer register into REG_0C */

iow(db, DM9000_EPAR, DM9000_PHY | reg);

/* Fill the written data into REG_0D & REG_0E */

iow(db, DM9000_EPDRL, value);

iow(db, DM9000_EPDRH, value >> 8);

/* Issue phyxcer write command */

iow(db, DM9000_EPCR, EPCR_EPOS | EPCR_ERPRW);

writeb(reg_save, db->io_addr);

spin_unlock_irqrestore(&db->lock, flags);

dm9000_msleep(db, 1); /* Wait write complete */

spin_lock_irqsave(&db->lock, flags);

reg_save = readb(db->io_addr);

iow(db, DM9000_EPCR, 0x0); /* Clear phyxcer write command */

/* restore the previous address */

writeb(reg_save, db->io_addr);

spin_unlock_irqrestore(&db->lock, flags);

mutex_unlock(&db->addr_lock);

}

/* dm9000_set_io

*

* select the specified set of io routines to use with the

* device

*/

static void dm9000_set_io(struct board_info *db, int byte_width)

{

/* use the size of the data resource to work out what IO

* routines we want to use

*/

switch (byte_width) {

case 1:

db->dumpblk = dm9000_dumpblk_8bit;

db->outblk = dm9000_outblk_8bit;

db->inblk = dm9000_inblk_8bit;

break;

case 3:

dev_dbg(db->dev, ": 3 byte IO, falling back to 16bitn");

case 2:

db->dumpblk = dm9000_dumpblk_16bit;

db->outblk = dm9000_outblk_16bit;

db->inblk = dm9000_inblk_16bit;

break;

case 4:

default:

db->dumpblk = dm9000_dumpblk_32bit;

db->outblk = dm9000_outblk_32bit;

db->inblk = dm9000_inblk_32bit;

break;

}

}

static void dm9000_schedule_poll(board_info_t *db)

{

if (db->type == TYPE_DM9000E)

schedule_delayed_work(&db->phy_poll, HZ * 2);

}

static int dm9000_ioctl(struct net_device *dev, struct ifreq *req, int cmd)

{

board_info_t *dm = to_dm9000_board(dev);

if (!netif_running(dev))

return -EINVAL;

return generic_mii_ioctl(&dm->mii, if_mii(req), cmd, NULL);

}

static unsigned int

dm9000_read_locked(board_info_t *db, int reg)

{

unsigned long flags;

unsigned int ret;

spin_lock_irqsave(&db->lock, flags);

ret = ior(db, reg);

spin_unlock_irqrestore(&db->lock, flags);

return ret;

}

static int dm9000_wait_eeprom(board_info_t *db)

{

unsigned int status;

int timeout = 8; /* wait max 8msec */

/* The DM9000 data sheets say we should be able to

* poll the ERRE bit in EPCR to wait for the EEPROM

* operation. From testing several chips, this bit

* does not seem to work.

*

* We attempt to use the bit, but fall back to the

* timeout (which is why we do not return an error

* on expiry) to say that the EEPROM operation has

* completed.

*/

while (1) {

status = dm9000_read_locked(db, DM9000_EPCR);

if ((status & EPCR_ERRE) == 0)

break;

msleep(1);

if (timeout-- < 0) {

dev_dbg(db->dev, "timeout waiting EEPROMn");

break;

}

}

return 0;

}

/*

* Read a word data from EEPROM

*/

static void

dm9000_read_eeprom(board_info_t *db, int offset, u8 *to)

{

unsigned long flags;

if (db->flags & DM9000_PLATF_NO_EEPROM) {

to[0] = 0xff;

to[1] = 0xff;

return;

}

mutex_lock(&db->addr_lock);

spin_lock_irqsave(&db->lock, flags);

iow(db, DM9000_EPAR, offset);

iow(db, DM9000_EPCR, EPCR_ERPRR);

spin_unlock_irqrestore(&db->lock, flags);

dm9000_wait_eeprom(db);

/* delay for at-least 150uS */

msleep(1);

spin_lock_irqsave(&db->lock, flags);

iow(db, DM9000_EPCR, 0x0);

to[0] = ior(db, DM9000_EPDRL);

to[1] = ior(db, DM9000_EPDRH);

spin_unlock_irqrestore(&db->lock, flags);

mutex_unlock(&db->addr_lock);

}

/*

* Write a word data to SROM

*/

static void

dm9000_write_eeprom(board_info_t *db, int offset, u8 *data)

{

unsigned long flags;

if (db->flags & DM9000_PLATF_NO_EEPROM)

return;

mutex_lock(&db->addr_lock);

spin_lock_irqsave(&db->lock, flags);

iow(db, DM9000_EPAR, offset);

iow(db, DM9000_EPDRH, data[1]);

iow(db, DM9000_EPDRL, data[0]);

iow(db, DM9000_EPCR, EPCR_WEP | EPCR_ERPRW);

spin_unlock_irqrestore(&db->lock, flags);

dm9000_wait_eeprom(db);

mdelay(1); /* wait at least 150uS to clear */

spin_lock_irqsave(&db->lock, flags);

iow(db, DM9000_EPCR, 0);

spin_unlock_irqrestore(&db->lock, flags);

mutex_unlock(&db->addr_lock);

}

/* ethtool ops */

static void dm9000_get_drvinfo(struct net_device *dev,

struct ethtool_drvinfo *info)

{

board_info_t *dm = to_dm9000_board(dev);

strlcpy(info->driver, CARDNAME, sizeof(info->driver));

strlcpy(info->version, DRV_VERSION, sizeof(info->version));

strlcpy(info->bus_info, to_platform_device(dm->dev)->name,

sizeof(info->bus_info));

}

static u32 dm9000_get_msglevel(struct net_device *dev)

{

board_info_t *dm = to_dm9000_board(dev);

return dm->msg_enable;

}

static void dm9000_set_msglevel(struct net_device *dev, u32 value)

{

board_info_t *dm = to_dm9000_board(dev);

dm->msg_enable = value;

}

static int dm9000_get_settings(struct net_device *dev, struct ethtool_cmd *cmd)

{

board_info_t *dm = to_dm9000_board(dev);

mii_ethtool_gset(&dm->mii, cmd);

return 0;

}

static int dm9000_set_settings(struct net_device *dev, struct ethtool_cmd *cmd)

{

board_info_t *dm = to_dm9000_board(dev);

return mii_ethtool_sset(&dm->mii, cmd);

}

static int dm9000_nway_reset(struct net_device *dev)

{

board_info_t *dm = to_dm9000_board(dev);

return mii_nway_restart(&dm->mii);

}

static int dm9000_set_features(struct net_device *dev,

netdev_features_t features)

{

board_info_t *dm = to_dm9000_board(dev);

netdev_features_t changed = dev->features ^ features;

unsigned long flags;

if (!(changed & NETIF_F_RXCSUM))

return 0;

spin_lock_irqsave(&dm->lock, flags);

iow(dm, DM9000_RCSR, (features & NETIF_F_RXCSUM) ? RCSR_CSUM : 0);

spin_unlock_irqrestore(&dm->lock, flags);

return 0;

}

static u32 dm9000_get_link(struct net_device *dev)

{

board_info_t *dm = to_dm9000_board(dev);

u32 ret;

if (dm->flags & DM9000_PLATF_EXT_PHY)

ret = mii_link_ok(&dm->mii);

else

ret = dm9000_read_locked(dm, DM9000_NSR) & NSR_LINKST ? 1 : 0;

return ret;

}

#define DM_EEPROM_MAGIC (0x444D394B)

static int dm9000_get_eeprom_len(struct net_device *dev)

{

return 128;

}

static int dm9000_get_eeprom(struct net_device *dev,

struct ethtool_eeprom *ee, u8 *data)

{

board_info_t *dm = to_dm9000_board(dev);

int offset = ee->offset;

int len = ee->len;

int i;

/* EEPROM access is aligned to two bytes */

if ((len & 1) != 0 || (offset & 1) != 0)

return -EINVAL;

if (dm->flags & DM9000_PLATF_NO_EEPROM)

return -ENOENT;

ee->magic = DM_EEPROM_MAGIC;

for (i = 0; i < len; i += 2)

dm9000_read_eeprom(dm, (offset + i) / 2, data + i);

return 0;

}

static int dm9000_set_eeprom(struct net_device *dev,

struct ethtool_eeprom *ee, u8 *data)

{

board_info_t *dm = to_dm9000_board(dev);

int offset = ee->offset;

int len = ee->len;

int done;

/* EEPROM access is aligned to two bytes */

if (dm->flags & DM9000_PLATF_NO_EEPROM)

return -ENOENT;

if (ee->magic != DM_EEPROM_MAGIC)

return -EINVAL;

while (len > 0) {

if (len & 1 || offset & 1) {

int which = offset & 1;

u8 tmp[2];

dm9000_read_eeprom(dm, offset / 2, tmp);

tmp[which] = *data;

dm9000_write_eeprom(dm, offset / 2, tmp);

done = 1;

} else {

dm9000_write_eeprom(dm, offset / 2, data);

done = 2;

}

data += done;

offset += done;

len -= done;

}

return 0;

}

static void dm9000_get_wol(struct net_device *dev, struct ethtool_wolinfo *w)

{

board_info_t *dm = to_dm9000_board(dev);

memset(w, 0, sizeof(struct ethtool_wolinfo));

/* note, we could probably support wake-phy too */

w->supported = dm->wake_supported ? WAKE_MAGIC : 0;

w->wolopts = dm->wake_state;

}

static int dm9000_set_wol(struct net_device *dev, struct ethtool_wolinfo *w)

{

board_info_t *dm = to_dm9000_board(dev);

unsigned long flags;

u32 opts = w->wolopts;

u32 wcr = 0;

if (!dm->wake_supported)

return -EOPNOTSUPP;

if (opts & ~WAKE_MAGIC)

return -EINVAL;

if (opts & WAKE_MAGIC)

wcr |= WCR_MAGICEN;

mutex_lock(&dm->addr_lock);

spin_lock_irqsave(&dm->lock, flags);

iow(dm, DM9000_WCR, wcr);

spin_unlock_irqrestore(&dm->lock, flags);

mutex_unlock(&dm->addr_lock);

if (dm->wake_state != opts) {

/* change in wol state, update IRQ state */

if (!dm->wake_state)

irq_set_irq_wake(dm->irq_wake, 1);

else if (dm->wake_state && !opts)

irq_set_irq_wake(dm->irq_wake, 0);

}

dm->wake_state = opts;

return 0;

}

static const struct ethtool_ops dm9000_ethtool_ops = {

.get_drvinfo = dm9000_get_drvinfo,

.get_settings = dm9000_get_settings,

.set_settings = dm9000_set_settings,

.get_msglevel = dm9000_get_msglevel,

.set_msglevel = dm9000_set_msglevel,

.nway_reset = dm9000_nway_reset,

.get_link = dm9000_get_link,

.get_wol = dm9000_get_wol,

.set_wol = dm9000_set_wol,

.get_eeprom_len = dm9000_get_eeprom_len,

.get_eeprom = dm9000_get_eeprom,

.set_eeprom = dm9000_set_eeprom,

};

static void dm9000_show_carrier(board_info_t *db,

unsigned carrier, unsigned nsr)

{

int lpa;

struct net_device *ndev = db->ndev;

struct mii_if_info *mii = &db->mii;

unsigned ncr = dm9000_read_locked(db, DM9000_NCR);

if (carrier) {

lpa = mii->mdio_read(mii->dev, mii->phy_id, MII_LPA);

dev_info(db->dev,

"%s: link up, %dMbps, %s-duplex, lpa 0x%04Xn",

ndev->name, (nsr & NSR_SPEED) ? 10 : 100,

(ncr & NCR_FDX) ? "full" : "half", lpa);

} else {

dev_info(db->dev, "%s: link downn", ndev->name);

}

}

static void

dm9000_poll_work(struct work_struct *w)

{

struct delayed_work *dw = to_delayed_work(w);

board_info_t *db = container_of(dw, board_info_t, phy_poll);

struct net_device *ndev = db->ndev;

if (db->flags & DM9000_PLATF_SIMPLE_PHY &&

!(db->flags & DM9000_PLATF_EXT_PHY)) {

unsigned nsr = dm9000_read_locked(db, DM9000_NSR);

unsigned old_carrier = netif_carrier_ok(ndev) ? 1 : 0;

unsigned new_carrier;

new_carrier = (nsr & NSR_LINKST) ? 1 : 0;

if (old_carrier != new_carrier) {

if (netif_msg_link(db))

dm9000_show_carrier(db, new_carrier, nsr);

if (!new_carrier)

netif_carrier_off(ndev);

else

netif_carrier_on(ndev);

}

} else

mii_check_media(&db->mii, netif_msg_link(db), 0);

if (netif_running(ndev))

dm9000_schedule_poll(db);

}

/* dm9000_release_board

*

* release a board, and any mapped resources

*/

static void

dm9000_release_board(struct platform_device *pdev, struct board_info *db)

{

/* unmap our resources */

iounmap(db->io_addr);

iounmap(db->io_data);

/* release the resources */

release_resource(db->data_req);

kfree(db->data_req);

release_resource(db->addr_req);

kfree(db->addr_req);

}

static unsigned char dm9000_type_to_char(enum dm9000_type type)

{

switch (type) {

case TYPE_DM9000E: return 'e';

case TYPE_DM9000A: return 'a';

case TYPE_DM9000B: return 'b';

}

return '?';

}

/*

* Set DM9000 multicast address

*/

static void

dm9000_hash_table_unlocked(struct net_device *dev)

{

board_info_t *db = netdev_priv(dev);

struct netdev_hw_addr *ha;

int i, oft;

u32 hash_val;

u16 hash_table[4] = { 0, 0, 0, 0x8000 }; /* broadcast address */

u8 rcr = RCR_DIS_LONG | RCR_DIS_CRC | RCR_RXEN;

dm9000_dbg(db, 1, "entering %sn", __func__);

for (i = 0, oft = DM9000_PAR; i < 6; i++, oft++)

iow(db, oft, dev->dev_addr[i]);

if (dev->flags & IFF_PROMISC)

rcr |= RCR_PRMSC;

if (dev->flags & IFF_ALLMULTI)

rcr |= RCR_ALL;

/* the multicast address in Hash Table : 64 bits */

netdev_for_each_mc_addr(ha, dev) {

hash_val = ether_crc_le(6, ha->addr) & 0x3f;

hash_table[hash_val / 16] |= (u16) 1 << (hash_val % 16);

}

/* Write the hash table to MAC MD table */

for (i = 0, oft = DM9000_MAR; i < 4; i++) {

iow(db, oft++, hash_table[i]);

iow(db, oft++, hash_table[i] >> 8);

}

iow(db, DM9000_RCR, rcr);

}

static void

dm9000_hash_table(struct net_device *dev)

{

board_info_t *db = netdev_priv(dev);

unsigned long flags;

spin_lock_irqsave(&db->lock, flags);

dm9000_hash_table_unlocked(dev);

spin_unlock_irqrestore(&db->lock, flags);

}

/*

* Initialize dm9000 board

*/

static void

dm9000_init_dm9000(struct net_device *dev)

{

board_info_t *db = netdev_priv(dev);

unsigned int imr;

unsigned int ncr;

dm9000_dbg(db, 1, "entering %sn", __func__);

/* I/O mode */

db->io_mode = ior(db, DM9000_ISR) >> 6; /* ISR bit7:6 keeps I/O mode */

/* Checksum mode */

if (dev->hw_features & NETIF_F_RXCSUM)

iow(db, DM9000_RCSR,

(dev->features & NETIF_F_RXCSUM) ? RCSR_CSUM : 0);

iow(db, DM9000_GPCR, GPCR_GEP_CNTL); /* Let GPIO0 output */

iow(db, DM9000_GPR, 0);

/* If we are dealing with DM9000B, some extra steps are required: a

* manual phy reset, and setting init params.

*/

if (db->type == TYPE_DM9000B) {

dm9000_phy_write(dev, 0, MII_BMCR, BMCR_RESET);

dm9000_phy_write(dev, 0, MII_DM_DSPCR, DSPCR_INIT_PARAM);

}

ncr = (db->flags & DM9000_PLATF_EXT_PHY) ? NCR_EXT_PHY : 0;

/* if wol is needed, then always set NCR_WAKEEN otherwise we end

* up dumping the wake events if we disable this. There is already

* a wake-mask in DM9000_WCR */

if (db->wake_supported)

ncr |= NCR_WAKEEN;

iow(db, DM9000_NCR, ncr);

/* Program operating register */

iow(db, DM9000_TCR, 0); /* TX Polling clear */

iow(db, DM9000_BPTR, 0x3f); /* Less 3Kb, 200us */

iow(db, DM9000_FCR, 0xff); /* Flow Control */

iow(db, DM9000_SMCR, 0); /* Special Mode */

/* clear TX status */

iow(db, DM9000_NSR, NSR_WAKEST | NSR_TX2END | NSR_TX1END);

iow(db, DM9000_ISR, ISR_CLR_STATUS); /* Clear interrupt status */

/* Set address filter table */

dm9000_hash_table_unlocked(dev);

imr = IMR_PAR | IMR_PTM | IMR_PRM;

if (db->type != TYPE_DM9000E)

imr |= IMR_LNKCHNG;

db->imr_all = imr;

/* Enable TX/RX interrupt mask */

iow(db, DM9000_IMR, imr);

/* Init Driver variable */

db->tx_pkt_cnt = 0;

db->queue_pkt_len = 0;

dev->trans_start = jiffies;

}

/* Our watchdog timed out. Called by the networking layer */

static void dm9000_timeout(struct net_device *dev)

{

board_info_t *db = netdev_priv(dev);

u8 reg_save;

unsigned long flags;

/* Save previous register address */

spin_lock_irqsave(&db->lock, flags);

reg_save = readb(db->io_addr);

netif_stop_queue(dev);

dm9000_reset(db);

dm9000_init_dm9000(dev);

/* We can accept TX packets again */

dev->trans_start = jiffies; /* prevent tx timeout */

netif_wake_queue(dev);

/* Restore previous register address */

writeb(reg_save, db->io_addr);

spin_unlock_irqrestore(&db->lock, flags);

}

static void dm9000_send_packet(struct net_device *dev,

int ip_summed,

u16 pkt_len)

{

board_info_t *dm = to_dm9000_board(dev);

/* The DM9000 is not smart enough to leave fragmented packets alone. */

if (dm->ip_summed != ip_summed) {

if (ip_summed == CHECKSUM_NONE)

iow(dm, DM9000_TCCR, 0);

else

iow(dm, DM9000_TCCR, TCCR_IP | TCCR_UDP | TCCR_TCP);

dm->ip_summed = ip_summed;

}

/* Set TX length to DM9000 */

iow(dm, DM9000_TXPLL, pkt_len);

iow(dm, DM9000_TXPLH, pkt_len >> 8);

/* Issue TX polling command */

iow(dm, DM9000_TCR, TCR_TXREQ); /* Cleared after TX complete */

}

/*

* Hardware start transmission.

* Send a packet to media from the upper layer.

*/

static int

dm9000_start_xmit(struct sk_buff *skb, struct net_device *dev)

{

unsigned long flags;

board_info_t *db = netdev_priv(dev);

dm9000_dbg(db, 3, "%s:n", __func__);

if (db->tx_pkt_cnt > 1)

return NETDEV_TX_BUSY;

spin_lock_irqsave(&db->lock, flags);

/* Move data to DM9000 TX RAM */

writeb(DM9000_MWCMD, db->io_addr);

(db->outblk)(db->io_data, skb->data, skb->len);

dev->stats.tx_bytes += skb->len;

db->tx_pkt_cnt++;

/* TX control: First packet immediately send, second packet queue */

if (db->tx_pkt_cnt == 1) {

dm9000_send_packet(dev, skb->ip_summed, skb->len);

} else {

/* Second packet */

db->queue_pkt_len = skb->len;

db->queue_ip_summed = skb->ip_summed;

netif_stop_queue(dev);

}

spin_unlock_irqrestore(&db->lock, flags);

/* free this SKB */

dev_kfree_skb(skb);

return NETDEV_TX_OK;

}

/*

* DM9000 interrupt handler

* receive the packet to upper layer, free the transmitted packet

*/

static void dm9000_tx_done(struct net_device *dev, board_info_t *db)

{

int tx_status = ior(db, DM9000_NSR); /* Got TX status */

if (tx_status & (NSR_TX2END | NSR_TX1END)) {

/* One packet sent complete */

db->tx_pkt_cnt--;

dev->stats.tx_packets++;

if (netif_msg_tx_done(db))

dev_dbg(db->dev, "tx done, NSR %02xn", tx_status);

/* Queue packet check & send */

if (db->tx_pkt_cnt > 0)

dm9000_send_packet(dev, db->queue_ip_summed,

db->queue_pkt_len);

netif_wake_queue(dev);

}

}

struct dm9000_rxhdr {

u8 RxPktReady;

u8 RxStatus;

__le16 RxLen;

} __packed;

/*

* Received a packet and pass to upper layer

*/

static void

dm9000_rx(struct net_device *dev)

{

board_info_t *db = netdev_priv(dev);

struct dm9000_rxhdr rxhdr;

struct sk_buff *skb;

u8 rxbyte, *rdptr;

bool GoodPacket;

int RxLen;

/* Check packet ready or not */

do {

ior(db, DM9000_MRCMDX); /* Dummy read */

/* Get most updated data */

rxbyte = readb(db->io_data);

/* Status check: this byte must be 0 or 1 */

if (rxbyte & DM9000_PKT_ERR) {

dev_warn(db->dev, "status check fail: %dn", rxbyte);

iow(db, DM9000_RCR, 0x00); /* Stop Device */

iow(db, DM9000_ISR, IMR_PAR); /* Stop INT request */

return;

}

if (!(rxbyte & DM9000_PKT_RDY))

return;

/* A packet ready now & Get status/length */

GoodPacket = true;

writeb(DM9000_MRCMD, db->io_addr);

(db->inblk)(db->io_data, &rxhdr, sizeof(rxhdr));

RxLen = le16_to_cpu(rxhdr.RxLen);

if (netif_msg_rx_status(db))

dev_dbg(db->dev, "RX: status %02x, length %04xn",

rxhdr.RxStatus, RxLen);

/* Packet Status check */

if (RxLen < 0x40) {

GoodPacket = false;

if (netif_msg_rx_err(db))

dev_dbg(db->dev, "RX: Bad Packet (runt)n");

}

if (RxLen > DM9000_PKT_MAX) {

dev_dbg(db->dev, "RST: RX Len:%xn", RxLen);

}

/* rxhdr.RxStatus is identical to RSR register. */

if (rxhdr.RxStatus & (RSR_FOE | RSR_CE | RSR_AE |

RSR_PLE | RSR_RWTO |

RSR_LCS | RSR_RF)) {

GoodPacket = false;

if (rxhdr.RxStatus & RSR_FOE) {

if (netif_msg_rx_err(db))

dev_dbg(db->dev, "fifo errorn");

dev->stats.rx_fifo_errors++;

}

if (rxhdr.RxStatus & RSR_CE) {

if (netif_msg_rx_err(db))

dev_dbg(db->dev, "crc errorn");

dev->stats.rx_crc_errors++;

}

if (rxhdr.RxStatus & RSR_RF) {

if (netif_msg_rx_err(db))

dev_dbg(db->dev, "length errorn");

dev->stats.rx_length_errors++;

}

}

/* Move data from DM9000 */

if (GoodPacket &&

((skb = netdev_alloc_skb(dev, RxLen + 4)) != NULL)) {

skb_reserve(skb, 2);

rdptr = (u8 *) skb_put(skb, RxLen - 4);

/* Read received packet from RX SRAM */

(db->inblk)(db->io_data, rdptr, RxLen);

dev->stats.rx_bytes += RxLen;

/* Pass to upper layer */

skb->protocol = eth_type_trans(skb, dev);

if (dev->features & NETIF_F_RXCSUM) {

if ((((rxbyte & 0x1c) << 3) & rxbyte) == 0)

skb->ip_summed = CHECKSUM_UNNECESSARY;

else

skb_checksum_none_assert(skb);

}

netif_rx(skb);

dev->stats.rx_packets++;

} else {

/* need to dump the packet's data */

(db->dumpblk)(db->io_data, RxLen);

}

} while (rxbyte & DM9000_PKT_RDY);

}

static irqreturn_t dm9000_interrupt(int irq, void *dev_id)

{

struct net_device *dev = dev_id;

board_info_t *db = netdev_priv(dev);

int int_status;

unsigned long flags;

u8 reg_save;

dm9000_dbg(db, 3, "entering %sn", __func__);

/* A real interrupt coming */

/* holders of db->lock must always block IRQs */

spin_lock_irqsave(&db->lock, flags);

/* Save previous register address */

reg_save = readb(db->io_addr);

/* Disable all interrupts */

iow(db, DM9000_IMR, IMR_PAR);

/* Got DM9000 interrupt status */

int_status = ior(db, DM9000_ISR); /* Got ISR */

iow(db, DM9000_ISR, int_status); /* Clear ISR status */

if (netif_msg_intr(db))

dev_dbg(db->dev, "interrupt status %02xn", int_status);

/* Received the coming packet */

if (int_status & ISR_PRS)

dm9000_rx(dev);

/* Trnasmit Interrupt check */

if (int_status & ISR_PTS)

dm9000_tx_done(dev, db);

if (db->type != TYPE_DM9000E) {

if (int_status & ISR_LNKCHNG) {

/* fire a link-change request */

schedule_delayed_work(&db->phy_poll, 1);

}

}

/* Re-enable interrupt mask */

iow(db, DM9000_IMR, db->imr_all);

/* Restore previous register address */

writeb(reg_save, db->io_addr);

spin_unlock_irqrestore(&db->lock, flags);

return IRQ_HANDLED;

}

static irqreturn_t dm9000_wol_interrupt(int irq, void *dev_id)

{

struct net_device *dev = dev_id;

board_info_t *db = netdev_priv(dev);

unsigned long flags;

unsigned nsr, wcr;

spin_lock_irqsave(&db->lock, flags);

nsr = ior(db, DM9000_NSR);

wcr = ior(db, DM9000_WCR);

dev_dbg(db->dev, "%s: NSR=0x%02x, WCR=0x%02xn", __func__, nsr, wcr);

if (nsr & NSR_WAKEST) {

/* clear, so we can avoid */

iow(db, DM9000_NSR, NSR_WAKEST);

if (wcr & WCR_LINKST)

dev_info(db->dev, "wake by link status changen");

if (wcr & WCR_SAMPLEST)

dev_info(db->dev, "wake by sample packetn");

if (wcr & WCR_MAGICST)

dev_info(db->dev, "wake by magic packetn");

if (!(wcr & (WCR_LINKST | WCR_SAMPLEST | WCR_MAGICST)))

dev_err(db->dev, "wake signalled with no reason? "

"NSR=0x%02x, WSR=0x%02xn", nsr, wcr);

}

spin_unlock_irqrestore(&db->lock, flags);

return (nsr & NSR_WAKEST) ? IRQ_HANDLED : IRQ_NONE;

}

#ifdef CONFIG_NET_POLL_CONTROLLER

/*

*Used by netconsole

*/

static void dm9000_poll_controller(struct net_device *dev)

{

disable_irq(dev->irq);

dm9000_interrupt(dev->irq, dev);

enable_irq(dev->irq);

}

#endif

/*

* Open the interface.

* The interface is opened whenever "ifconfig" actives it.

*/

static int

dm9000_open(struct net_device *dev)

{

board_info_t *db = netdev_priv(dev);

unsigned long irqflags = db->irq_res->flags & IRQF_TRIGGER_MASK;

if (netif_msg_ifup(db))

dev_dbg(db->dev, "enabling %sn", dev->name);

/* If there is no IRQ type specified, default to something that

* may work, and tell the user that this is a problem */

if (irqflags == IRQF_TRIGGER_NONE)

dev_warn(db->dev, "WARNING: no IRQ resource flags set.n");

irqflags |= IRQF_SHARED;

/* GPIO0 on pre-activate PHY, Reg 1F is not set by reset */

iow(db, DM9000_GPR, 0); /* REG_1F bit0 activate phyxcer */

mdelay(1); /* delay needs by DM9000B */

/* Initialize DM9000 board */

dm9000_reset(db);

dm9000_init_dm9000(dev);

if (request_irq(dev->irq, dm9000_interrupt, irqflags, dev->name, dev))

return -EAGAIN;

/* Init driver variable */

db->dbug_cnt = 0;

mii_check_media(&db->mii, netif_msg_link(db), 1);

netif_start_queue(dev);

dm9000_schedule_poll(db);

return 0;

}

static void

dm9000_shutdown(struct net_device *dev)

{

board_info_t *db = netdev_priv(dev);

/* RESET device */

dm9000_phy_write(dev, 0, MII_BMCR, BMCR_RESET); /* PHY RESET */

iow(db, DM9000_GPR, 0x01); /* Power-Down PHY */

iow(db, DM9000_IMR, IMR_PAR); /* Disable all interrupt */

iow(db, DM9000_RCR, 0x00); /* Disable RX */

}

/*

* Stop the interface.

* The interface is stopped when it is brought.

*/

static int

dm9000_stop(struct net_device *ndev)

{

board_info_t *db = netdev_priv(ndev);

if (netif_msg_ifdown(db))

dev_dbg(db->dev, "shutting down %sn", ndev->name);

cancel_delayed_work_sync(&db->phy_poll);

netif_stop_queue(ndev);

netif_carrier_off(ndev);

/* free interrupt */

free_irq(ndev->irq, ndev);

dm9000_shutdown(ndev);

return 0;

}

static const struct net_device_ops dm9000_netdev_ops = {

.ndo_open = dm9000_open,

.ndo_stop = dm9000_stop,

.ndo_start_xmit = dm9000_start_xmit,

.ndo_tx_timeout = dm9000_timeout,

.ndo_set_rx_mode = dm9000_hash_table,

.ndo_do_ioctl = dm9000_ioctl,

.ndo_change_mtu = eth_change_mtu,

.ndo_set_features = dm9000_set_features,

.ndo_validate_addr = eth_validate_addr,

.ndo_set_mac_address = eth_mac_addr,

#ifdef CONFIG_NET_POLL_CONTROLLER

.ndo_poll_controller = dm9000_poll_controller,

#endif

};

static struct dm9000_plat_data *dm9000_parse_dt(struct device *dev)

{

struct dm9000_plat_data *pdata;

struct device_node *np = dev->of_node;

const void *mac_addr;

if (!IS_ENABLED(CONFIG_OF) || !np)

return NULL;

pdata = devm_kzalloc(dev, sizeof(*pdata), GFP_KERNEL);

if (!pdata)

return ERR_PTR(-ENOMEM);

if (of_find_property(np, "davicom,ext-phy", NULL))

pdata->flags |= DM9000_PLATF_EXT_PHY;

if (of_find_property(np, "davicom,no-eeprom", NULL))

pdata->flags |= DM9000_PLATF_NO_EEPROM;

mac_addr = of_get_mac_address(np);

if (mac_addr)

memcpy(pdata->dev_addr, mac_addr, sizeof(pdata->dev_addr));

return pdata;

}

/*

* Search DM9000 board, allocate space and register it

*/

static int

dm9000_probe(struct platform_device *pdev)

{

struct dm9000_plat_data *pdata = dev_get_platdata(&pdev->dev);

struct board_info *db; /* Point a board information structure */

struct net_device *ndev;

const unsigned char *mac_src;

int ret = 0;

int iosize;

int i;

u32 id_val;

if (!pdata) {

pdata = dm9000_parse_dt(&pdev->dev);

if (IS_ERR(pdata))

return PTR_ERR(pdata);

}

/* Init network device */

ndev = alloc_etherdev(sizeof(struct board_info));

if (!ndev)

return -ENOMEM;

SET_NETDEV_DEV(ndev, &pdev->dev);

dev_dbg(&pdev->dev, "dm9000_probe()n");

/* setup board info structure */

db = netdev_priv(ndev);

db->dev = &pdev->dev;

db->ndev = ndev;

spin_lock_init(&db->lock);

mutex_init(&db->addr_lock);

INIT_DELAYED_WORK(&db->phy_poll, dm9000_poll_work);

db->addr_res = platform_get_resource(pdev, IORESOURCE_MEM, 0);

db->data_res = platform_get_resource(pdev, IORESOURCE_MEM, 1);

db->irq_res = platform_get_resource(pdev, IORESOURCE_IRQ, 0);

if (db->addr_res == NULL || db->data_res == NULL ||

db->irq_res == NULL) {

dev_err(db->dev, "insufficient resourcesn");

ret = -ENOENT;

goto out;

}

db->irq_wake = platform_get_irq(pdev, 1);

if (db->irq_wake >= 0) {

dev_dbg(db->dev, "wakeup irq %dn", db->irq_wake);

ret = request_irq(db->irq_wake, dm9000_wol_interrupt,

IRQF_SHARED, dev_name(db->dev), ndev);

if (ret) {

dev_err(db->dev, "cannot get wakeup irq (%d)n", ret);

} else {

/* test to see if irq is really wakeup capable */

ret = irq_set_irq_wake(db->irq_wake, 1);

if (ret) {

dev_err(db->dev, "irq %d cannot set wakeup (%d)n",

db->irq_wake, ret);

ret = 0;

} else {

irq_set_irq_wake(db->irq_wake, 0);

db->wake_supported = 1;

}

}

}

iosize = resource_size(db->addr_res);

db->addr_req = request_mem_region(db->addr_res->start, iosize,

pdev->name);

if (db->addr_req == NULL) {

dev_err(db->dev, "cannot claim address reg arean");

ret = -EIO;

goto out;

}

db->io_addr = ioremap(db->addr_res->start, iosize);

if (db->io_addr == NULL) {

dev_err(db->dev, "failed to ioremap address regn");

ret = -EINVAL;

goto out;

}

iosize = resource_size(db->data_res);

db->data_req = request_mem_region(db->data_res->start, iosize,

pdev->name);

if (db->data_req == NULL) {

dev_err(db->dev, "cannot claim data reg arean");

ret = -EIO;

goto out;

}

db->io_data = ioremap(db->data_res->start, iosize);

if (db->io_data == NULL) {

dev_err(db->dev, "failed to ioremap data regn");

ret = -EINVAL;

goto out;

}

/* fill in parameters for net-dev structure */

ndev->base_addr = (unsigned long)db->io_addr;

ndev->irq = db->irq_res->start;

/* ensure at least we have a default set of IO routines */

dm9000_set_io(db, iosize);

/* check to see if anything is being over-ridden */

if (pdata != NULL) {

/* check to see if the driver wants to over-ride the

* default IO width */

if (pdata->flags & DM9000_PLATF_8BITONLY)

dm9000_set_io(db, 1);

if (pdata->flags & DM9000_PLATF_16BITONLY)

dm9000_set_io(db, 2);

if (pdata->flags & DM9000_PLATF_32BITONLY)

dm9000_set_io(db, 4);

/* check to see if there are any IO routine

* over-rides */

if (pdata->inblk != NULL)

db->inblk = pdata->inblk;

if (pdata->outblk != NULL)

db->outblk = pdata->outblk;

if (pdata->dumpblk != NULL)

db->dumpblk = pdata->dumpblk;

db->flags = pdata->flags;

}

#ifdef CONFIG_DM9000_FORCE_SIMPLE_PHY_POLL

db->flags |= DM9000_PLATF_SIMPLE_PHY;

#endif

/* Fixing bug on dm9000_probe, takeover dm9000_reset(db),

* Need 'NCR_MAC_LBK' bit to indeed stable our DM9000 fifo

* while probe stage.

*/

iow(db, DM9000_NCR, NCR_MAC_LBK | NCR_RST);

/* try multiple times, DM9000 sometimes gets the read wrong */

for (i = 0; i < 8; i++) {

id_val = ior(db, DM9000_VIDL);

id_val |= (u32)ior(db, DM9000_VIDH) << 8;

id_val |= (u32)ior(db, DM9000_PIDL) << 16;

id_val |= (u32)ior(db, DM9000_PIDH) << 24;

if (id_val == DM9000_ID)

break;

dev_err(db->dev, "read wrong id 0x%08xn", id_val);

}

if (id_val != DM9000_ID) {

dev_err(db->dev, "wrong id: 0x%08xn", id_val);

ret = -ENODEV;

goto out;

}

/* Identify what type of DM9000 we are working on */

id_val = ior(db, DM9000_CHIPR);

dev_dbg(db->dev, "dm9000 revision 0x%02xn", id_val);

switch (id_val) {

case CHIPR_DM9000A:

db->type = TYPE_DM9000A;

break;

case CHIPR_DM9000B:

db->type = TYPE_DM9000B;

break;

default:

dev_dbg(db->dev, "ID %02x => defaulting to DM9000En", id_val);

db->type = TYPE_DM9000E;

}

/* dm9000a/b are capable of hardware checksum offload */

if (db->type == TYPE_DM9000A || db->type == TYPE_DM9000B) {

ndev->hw_features = NETIF_F_RXCSUM | NETIF_F_IP_CSUM;

ndev->features |= ndev->hw_features;

}

/* from this point we assume that we have found a DM9000 */

/* driver system function */

ether_setup(ndev);

ndev->netdev_ops = &dm9000_netdev_ops;

ndev->watchdog_timeo = msecs_to_jiffies(watchdog);

ndev->ethtool_ops = &dm9000_ethtool_ops;

db->msg_enable = NETIF_MSG_LINK;

db->mii.phy_id_mask = 0x1f;

db->mii.reg_num_mask = 0x1f;

db->mii.force_media = 0;

db->mii.full_duplex = 0;

db->mii.dev = ndev;

db->mii.mdio_read = dm9000_phy_read;

db->mii.mdio_write = dm9000_phy_write;

mac_src = "eeprom";

/* try reading the node address from the attached EEPROM */

for (i = 0; i < 6; i += 2)

dm9000_read_eeprom(db, i / 2, ndev->dev_addr+i);

if (!is_valid_ether_addr(ndev->dev_addr) && pdata != NULL) {

mac_src = "platform data";

memcpy(ndev->dev_addr, pdata->dev_addr, ETH_ALEN);

}

if (!is_valid_ether_addr(ndev->dev_addr)) {

/* try reading from mac */

mac_src = "chip";

for (i = 0; i < 6; i++)

ndev->dev_addr[i] = ior(db, i+DM9000_PAR);

}

if (!is_valid_ether_addr(ndev->dev_addr)) {

dev_warn(db->dev, "%s: Invalid ethernet MAC address. Please "

"set using ifconfign", ndev->name);

eth_hw_addr_random(ndev);

mac_src = "random";

}

platform_set_drvdata(pdev, ndev);

ret = register_netdev(ndev);

if (ret == 0)

printk(KERN_INFO "%s: dm9000%c at %p,%p IRQ %d MAC: %pM (%s)n",

ndev->name, dm9000_type_to_char(db->type),

db->io_addr, db->io_data, ndev->irq,

ndev->dev_addr, mac_src);

return 0;

out:

dev_err(db->dev, "not found (%d).n", ret);

dm9000_release_board(pdev, db);

free_netdev(ndev);

return ret;

}

static int

dm9000_drv_suspend(struct device *dev)

{

struct platform_device *pdev = to_platform_device(dev);

struct net_device *ndev = platform_get_drvdata(pdev);

board_info_t *db;

if (ndev) {

db = netdev_priv(ndev);

db->in_suspend = 1;

if (!netif_running(ndev))

return 0;

netif_device_detach(ndev);

/* only shutdown if not using WoL */

if (!db->wake_state)

dm9000_shutdown(ndev);

}

return 0;

}

static int

dm9000_drv_resume(struct device *dev)

{

struct platform_device *pdev = to_platform_device(dev);

struct net_device *ndev = platform_get_drvdata(pdev);

board_info_t *db = netdev_priv(ndev);

if (ndev) {

if (netif_running(ndev)) {

/* reset if we were not in wake mode to ensure if

* the device was powered off it is in a known state */

if (!db->wake_state) {

dm9000_reset(db);

dm9000_init_dm9000(ndev);

}

netif_device_attach(ndev);

}

db->in_suspend = 0;

}

return 0;

}

static const struct dev_pm_ops dm9000_drv_pm_ops = {

.suspend = dm9000_drv_suspend,

.resume = dm9000_drv_resume,

};

static int

dm9000_drv_remove(struct platform_device *pdev)

{

struct net_device *ndev = platform_get_drvdata(pdev);

unregister_netdev(ndev);

dm9000_release_board(pdev, netdev_priv(ndev));

free_netdev(ndev); /* free device structure */

dev_dbg(&pdev->dev, "released and freed devicen");

return 0;

}

#ifdef CONFIG_OF

static const struct of_device_id dm9000_of_matches[] = {

{ .compatible = "davicom,dm9000", },

{ /* sentinel */ }

};

MODULE_DEVICE_TABLE(of, dm9000_of_matches);

#endif

static struct platform_driver dm9000_driver = {

.driver = {

.name = "dm9000",

.owner = THIS_MODULE,

.pm = &dm9000_drv_pm_ops,

.of_match_table = of_match_ptr(dm9000_of_matches),

},

.probe = dm9000_probe,

.remove = dm9000_drv_remove,

};

module_platform_driver(dm9000_driver);

MODULE_AUTHOR("Sascha Hauer, Ben Dooks");

MODULE_DESCRIPTION("Davicom DM9000 network driver");

MODULE_LICENSE("GPL");

MODULE_ALIAS("platform:dm9000");

好好好又是ben,coeddump机制就是这小子写的,我之前实习的时候也叫这个,真是有缘。

在 dm9000_probe 函数中,代码第 1421 行,函数一开始使用 alloc_etherdev分配了网络设备对象的内存,并使用 netdev_priv 得到了私有数据的起始地址。

代码第 1440行至第 1442 行分别获取了两个寄存器的地址和中断号,然后使用ioremap 对这两个寄存器进行了映射,最后将 I/O 端口地址记录在设备对象的 base_addr成员中,将中断号记录在了设备对象的 irg 成员中。

接下来设置了端口数据总线的宽度,因为 DM9000 是一个系列的芯片,有的宽度是8 位,有的宽度是 16 位,也有宽度是 32 位的,FS4412 目标板使用的是 16 位。在数密位宽设定好了后,就可以对设备进行访问,以判断硬件是否真实存在。

(1558~1590)代码先多次读取 DM9000 的 ID 号(因为前面几次读取可能会失败),然后再判断 ID 号是否正确,如果正确,那么说明硬件存在,继续读取芯片的类型 ID,并根据该ID做进一步的设置。这里用到的 ior 宏是先将 DM9000 内部存器的地址写入到地址寄存器中,然后再读数据寄存器,iow 宏有类似的过程,只是后面是写数据寄存器。这样就可以通过两个寄存器来访问 DM9000 内部的 256 个寄存器。

(1601~1645)接下来使用了 ether_setup 又一次初始化了设备对象 ndev,然后将操作方法集、发送超时和 ethtool 对应的接口分别进行了初始化。代码第 1608 行至第 1614 行是与 PHY 相关的初始化,因为 DM9000内部集成了一个 PHY(以太网通信链路层全部功能的器件),后面又使用几种方法来尝试获得 MAC地址,如果都失败了就随机生成一个MAC 地址,最后使用reister_netdev 注册了网设备。在 dm9000_probe 函数中还使用 INIT_DELAYED_WORK(&db_phy_poll, dm900_poll_work)初始化了一个延时函数 dm9000_poll_work。这个函数用于定期检测网线的连接状态,在网卡激活时启动该函数,在网卡禁止时停止该检测.

接下来我们还是主要关注 DM9000 网络设备的激活、停止、发送数包和接收数据包的部分。DM9000 网络设备激活的函数是 dm9000_open,

(1282~1319)

代码第 1300 行激活了 PHY。代码第 1304 行和第 1305 行复位并初始化了 DM9000芯片。代码第 1307 行注册了中断处理函数 dm9000_interrupt。最后启动了队列并调度了延时工作函数 dm9000_poll_work 的运行。

DM9000 网络设备禁止的函数是 dm9000_stop,它的工作刚好和激活函数相反,这就不再列出代码了

DM9000 网络设备的数据包发送函数是 dm9000_start_xmit,代码(1003~1039).

DM9000 内部采用双缓冲机制,可以同时将两个待发送的数据包写入 DM9000 芯片后再依次发送。代码第 1011 行首先判断 DM9000 内部的两个缓冲区是否都被占用,如果是则返回忙。如果不是,那么在代码第 1017 行至第 1020 行就将数据包写入 DM900内部的缓冲区。如果目前只有一个缓冲区被占用,那么在代码第 1025 行马上启动数据包的发送;如果两个缓冲区都被占用,则记录好信息,并且停止队列。最后释放包含发送数据包的 skb。当数据包发送完成后,DM9000 会产生一个发送中断,这会导致前面注册的中断处理函数被调用,在中断处理函数中进一步调用 dm9000_tx_done函数,代码见(1046~1064)

代码主要对发送统计行了维护,如果 DM9000 内部还有一个缓冲区的数据未发送则立即启动下一个数据包的发送。接下来调用了 netif_wake_queue 函数重新启动了队列,这样就完成了流控操作。

当 DM9000 接收到数据包后会产生中断,导致中断处理函数被调用,中断处理函数进一步调用 dm9000_rx 函数来完成对接收数据包的处理,代码见(1075~1176)。

在 dm9000_rx 函数中,首先对数据包的正确性做了判断,,如果数据包是好的,那么使用 netdev_alloc_skb 分配了 skb,然后在代码第 1156 行将数据包从 DM9000 内部的接收缓冲区中读入了 skb 中。代码第 1160 行设置了数据包的数据链路层的协议后,在代码第1167 行使用 netif_rx 递交了数据包,并维护了接收统计计数信息。在 dm9000_rx 函数中当处理完一个数据包后,要判断是否还有数据包未处理,如果有则继续处理,直到所有的数据包都处理完。

另外,当发送数据包超时时,dm9000_timeout 超时函数将会被调用。在该函数中最主要的就是复位并重新初始化了 DM9000 芯片。

可以发现,DM9000 网络设备驱动除了硬件处理的细节,主体框架和我们上一节实现的虚拟网络设备驱动是一样的。

六、NAPI

一直以来,中断都意味着高效的处理,因为现在 I/O 的速度一般远远低于 CPU 的处理速度。如果让 CPU 轮询 I/O 的状态,在 I/O 准备好的情况下再进行处理的话,大量宝贵的 CPU 时间被浪费在无谓的轮询等待上,这显然是不合适的。所以,普遍的教科书都一致推荐使用中断来代替轮询。但是,如果中断非常频繁地发生,中断的机制不一定会比轮询具有更高的效率。因为中断进入和退出需要保护现场和恢复现场,频繁发生的中断将会导致在这方面的处理太消耗时间,轮询反而是更合适的选择。在这种情况下每次轮询几乎都会成功,也就不存在等待的时间消耗了。现在千兆以太网已经很常见,人们对高带宽的要求也是越来越强烈,短期密集型数据包的到来的情况越来越多。为了适应这一情况,Linux 开发了 NAPI(New API) 机制,这种机制的实现思想也非常直观:以轮询为主,以中断为辅。平时设备以中断方式进行工作,接收到数据包后先进入中断处理函数进行处理,然后转为轮询的方式进行工作,持续接收后续的数据包,满足一定的条件后退出轮询模式,再以中断的方式进行工作。

但不是每一个网络设备都能实现 NAPI机制,必须要满足以下两个条件:

(1) 设备能够保留多个接收到的数据包,如多缓冲机制。否则,后面新到来的数据包将会被丢弃,进入轮询模式后也就没有意义了。

(2)能独立禁止接收数据包产生的中断。否则如果将其他中断也禁止,将会严重影响其他设备的工作。

为了支持NAPI机制,内核引入了新的数据结构 struct napi_struct,定义如下。

306 struct napi_struct {

307 /* The poll_list must only be managed by the entity which

308 * changes the state of the NAPI_STATE_SCHED bit. This means

309 * whoever atomically sets that bit can add this napi_struct

310 * to the per-cpu poll_list, and whoever clears that bit

311 * can remove from the list right before clearing the bit.

312 */

313 struct list_head poll_list;

314

315 unsigned long state;

316 int weight;

317 unsigned int gro_count;

318 int (*poll)(struct napi_struct *, int);

319 #ifdef CONFIG_NETPOLL

320 spinlock_t poll_lock;

321 int poll_owner;

322 #endif

323 struct net_device *dev;

324 struct sk_buff *gro_list;

325 struct sk_buff *skb;

326 struct list_head dev_list;

327 struct hlist_node napi_hash_node;

328 unsigned int napi_id;

329 };

最重要的成员有 3 个,分别是 poll_list、weight 和 poll,其中 poll_list 将所有要轮询的网络设备通过链表链接起来,weight 是该设备被轮询的时间的一个权重。也就是说,如果系统中有多个网络设备都实现了 NAPI,那么内核将会轮询这个链表中的每一个设备,而每个设备轮询多长时间是由 weight 这个权重来决定的。当轮询一个具体的设备时又会进一步轮询多个接收的数据包。所以完整的轮询有两个层次,先是设备这一层次,然后是一个设备的多个接收数据包这一层次。poll 是指向网络设备驱动实现的轮询函数的指针。围绕这个结构,有下面一些函数。

void netif_napi_add(struct net_device *dev,struct napi_struct *napi, int (*poll)(struct napi_struct *, int),int weight);

void netif_napi_del(struct napi_struct *napi);

void napi_enable(struct napi_struct *n);

void napi_disable(struct napi_struct *n);

void napi_schedule(struct napi_struct *n);

void napi_complete(struct napi_struct *n);上面函数的含义都比较直观,这里就不再一一介绍了。接下来以 drivers/net/ethemmevrealtek/r8169.c 驱动代码为例来说明 NAPI的使用方法。

/*

* r8169.c: RealTek 8169/8168/8101 ethernet driver.

*

* Copyright (c) 2002 ShuChen <shuchen@realtek.com.tw>

* Copyright (c) 2003 - 2007 Francois Romieu <romieu@fr.zoreil.com>

* Copyright (c) a lot of people too. Please respect their work.

*

* See MAINTAINERS file for support contact information.

*/

#include <linux/module.h>

#include <linux/moduleparam.h>

#include <linux/pci.h>

#include <linux/netdevice.h>

#include <linux/etherdevice.h>

#include <linux/delay.h>

#include <linux/ethtool.h>

#include <linux/mii.h>

#include <linux/if_vlan.h>

#include <linux/crc32.h>

#include <linux/in.h>

#include <linux/ip.h>

#include <linux/tcp.h>

#include <linux/interrupt.h>

#include <linux/dma-mapping.h>

#include <linux/pm_runtime.h>

#include <linux/firmware.h>

#include <linux/pci-aspm.h>

#include <linux/prefetch.h>

#include <asm/io.h>

#include <asm/irq.h>

#define RTL8169_VERSION "2.3LK-NAPI"

#define MODULENAME "r8169"

#define PFX MODULENAME ": "

#define FIRMWARE_8168D_1 "rtl_nic/rtl8168d-1.fw"

#define FIRMWARE_8168D_2 "rtl_nic/rtl8168d-2.fw"

#define FIRMWARE_8168E_1 "rtl_nic/rtl8168e-1.fw"

#define FIRMWARE_8168E_2 "rtl_nic/rtl8168e-2.fw"

#define FIRMWARE_8168E_3 "rtl_nic/rtl8168e-3.fw"

#define FIRMWARE_8168F_1 "rtl_nic/rtl8168f-1.fw"

#define FIRMWARE_8168F_2 "rtl_nic/rtl8168f-2.fw"

#define FIRMWARE_8105E_1 "rtl_nic/rtl8105e-1.fw"

#define FIRMWARE_8402_1 "rtl_nic/rtl8402-1.fw"

#define FIRMWARE_8411_1 "rtl_nic/rtl8411-1.fw"

#define FIRMWARE_8411_2 "rtl_nic/rtl8411-2.fw"

#define FIRMWARE_8106E_1 "rtl_nic/rtl8106e-1.fw"

#define FIRMWARE_8106E_2 "rtl_nic/rtl8106e-2.fw"

#define FIRMWARE_8168G_2 "rtl_nic/rtl8168g-2.fw"

#define FIRMWARE_8168G_3 "rtl_nic/rtl8168g-3.fw"

#ifdef RTL8169_DEBUG

#define assert(expr)

if (!(expr)) {

printk( "Assertion failed! %s,%s,%s,line=%dn",

#expr,__FILE__,__func__,__LINE__);

}

#define dprintk(fmt, args...)

do { printk(KERN_DEBUG PFX fmt, ## args); } while (0)

#else

#define assert(expr) do {} while (0)

#define dprintk(fmt, args...) do {} while (0)

#endif /* RTL8169_DEBUG */

#define R8169_MSG_DEFAULT

(NETIF_MSG_DRV | NETIF_MSG_PROBE | NETIF_MSG_IFUP | NETIF_MSG_IFDOWN)

#define TX_SLOTS_AVAIL(tp)

(tp->dirty_tx + NUM_TX_DESC - tp->cur_tx)

/* A skbuff with nr_frags needs nr_frags+1 entries in the tx queue */

#define TX_FRAGS_READY_FOR(tp,nr_frags)

(TX_SLOTS_AVAIL(tp) >= (nr_frags + 1))

/* Maximum number of multicast addresses to filter (vs. Rx-all-multicast).

The RTL chips use a 64 element hash table based on the Ethernet CRC. */

static const int multicast_filter_limit = 32;

#define MAX_READ_REQUEST_SHIFT 12

#define TX_DMA_BURST 7 /* Maximum PCI burst, '7' is unlimited */

#define InterFrameGap 0x03 /* 3 means InterFrameGap = the shortest one */

#define R8169_REGS_SIZE 256

#define R8169_NAPI_WEIGHT 64

#define NUM_TX_DESC 64 /* Number of Tx descriptor registers */

#define NUM_RX_DESC 256U /* Number of Rx descriptor registers */

#define R8169_TX_RING_BYTES (NUM_TX_DESC * sizeof(struct TxDesc))

#define R8169_RX_RING_BYTES (NUM_RX_DESC * sizeof(struct RxDesc))

#define RTL8169_TX_TIMEOUT (6*HZ)

#define RTL8169_PHY_TIMEOUT (10*HZ)

/* write/read MMIO register */

#define RTL_W8(reg, val8) writeb ((val8), ioaddr + (reg))

#define RTL_W16(reg, val16) writew ((val16), ioaddr + (reg))

#define RTL_W32(reg, val32) writel ((val32), ioaddr + (reg))

#define RTL_R8(reg) readb (ioaddr + (reg))

#define RTL_R16(reg) readw (ioaddr + (reg))

#define RTL_R32(reg) readl (ioaddr + (reg))

enum mac_version {

RTL_GIGA_MAC_VER_01 = 0,

RTL_GIGA_MAC_VER_02,

RTL_GIGA_MAC_VER_03,

RTL_GIGA_MAC_VER_04,

RTL_GIGA_MAC_VER_05,

RTL_GIGA_MAC_VER_06,

RTL_GIGA_MAC_VER_07,

RTL_GIGA_MAC_VER_08,

RTL_GIGA_MAC_VER_09,

RTL_GIGA_MAC_VER_10,

RTL_GIGA_MAC_VER_11,

RTL_GIGA_MAC_VER_12,

RTL_GIGA_MAC_VER_13,

RTL_GIGA_MAC_VER_14,

RTL_GIGA_MAC_VER_15,

RTL_GIGA_MAC_VER_16,

RTL_GIGA_MAC_VER_17,

RTL_GIGA_MAC_VER_18,

RTL_GIGA_MAC_VER_19,

RTL_GIGA_MAC_VER_20,

RTL_GIGA_MAC_VER_21,

RTL_GIGA_MAC_VER_22,

RTL_GIGA_MAC_VER_23,

RTL_GIGA_MAC_VER_24,

RTL_GIGA_MAC_VER_25,

RTL_GIGA_MAC_VER_26,

RTL_GIGA_MAC_VER_27,

RTL_GIGA_MAC_VER_28,

RTL_GIGA_MAC_VER_29,

RTL_GIGA_MAC_VER_30,

RTL_GIGA_MAC_VER_31,

RTL_GIGA_MAC_VER_32,

RTL_GIGA_MAC_VER_33,

RTL_GIGA_MAC_VER_34,

RTL_GIGA_MAC_VER_35,

RTL_GIGA_MAC_VER_36,

RTL_GIGA_MAC_VER_37,

RTL_GIGA_MAC_VER_38,

RTL_GIGA_MAC_VER_39,

RTL_GIGA_MAC_VER_40,

RTL_GIGA_MAC_VER_41,

RTL_GIGA_MAC_VER_42,

RTL_GIGA_MAC_VER_43,

RTL_GIGA_MAC_VER_44,

RTL_GIGA_MAC_NONE = 0xff,

};

enum rtl_tx_desc_version {

RTL_TD_0 = 0,

RTL_TD_1 = 1,

};

#define JUMBO_1K ETH_DATA_LEN

#define JUMBO_4K (4*1024 - ETH_HLEN - 2)

#define JUMBO_6K (6*1024 - ETH_HLEN - 2)

#define JUMBO_7K (7*1024 - ETH_HLEN - 2)

#define JUMBO_9K (9*1024 - ETH_HLEN - 2)

#define _R(NAME,TD,FW,SZ,B) {

.name = NAME,

.txd_version = TD,

.fw_name = FW,

.jumbo_max = SZ,

.jumbo_tx_csum = B

}

static const struct {

const char *name;

enum rtl_tx_desc_version txd_version;

const char *fw_name;

u16 jumbo_max;

bool jumbo_tx_csum;

} rtl_chip_infos[] = {

/* PCI devices. */

[RTL_GIGA_MAC_VER_01] =

_R("RTL8169", RTL_TD_0, NULL, JUMBO_7K, true),

[RTL_GIGA_MAC_VER_02] =

_R("RTL8169s", RTL_TD_0, NULL, JUMBO_7K, true),

[RTL_GIGA_MAC_VER_03] =

_R("RTL8110s", RTL_TD_0, NULL, JUMBO_7K, true),

[RTL_GIGA_MAC_VER_04] =

_R("RTL8169sb/8110sb", RTL_TD_0, NULL, JUMBO_7K, true),

[RTL_GIGA_MAC_VER_05] =

_R("RTL8169sc/8110sc", RTL_TD_0, NULL, JUMBO_7K, true),

[RTL_GIGA_MAC_VER_06] =

_R("RTL8169sc/8110sc", RTL_TD_0, NULL, JUMBO_7K, true),

/* PCI-E devices. */

[RTL_GIGA_MAC_VER_07] =

_R("RTL8102e", RTL_TD_1, NULL, JUMBO_1K, true),

[RTL_GIGA_MAC_VER_08] =

_R("RTL8102e", RTL_TD_1, NULL, JUMBO_1K, true),

[RTL_GIGA_MAC_VER_09] =

_R("RTL8102e", RTL_TD_1, NULL, JUMBO_1K, true),

[RTL_GIGA_MAC_VER_10] =

_R("RTL8101e", RTL_TD_0, NULL, JUMBO_1K, true),

[RTL_GIGA_MAC_VER_11] =

_R("RTL8168b/8111b", RTL_TD_0, NULL, JUMBO_4K, false),

[RTL_GIGA_MAC_VER_12] =

_R("RTL8168b/8111b", RTL_TD_0, NULL, JUMBO_4K, false),

[RTL_GIGA_MAC_VER_13] =

_R("RTL8101e", RTL_TD_0, NULL, JUMBO_1K, true),

[RTL_GIGA_MAC_VER_14] =

_R("RTL8100e", RTL_TD_0, NULL, JUMBO_1K, true),

[RTL_GIGA_MAC_VER_15] =

_R("RTL8100e", RTL_TD_0, NULL, JUMBO_1K, true),

[RTL_GIGA_MAC_VER_16] =

_R("RTL8101e", RTL_TD_0, NULL, JUMBO_1K, true),

[RTL_GIGA_MAC_VER_17] =

_R("RTL8168b/8111b", RTL_TD_0, NULL, JUMBO_4K, false),

[RTL_GIGA_MAC_VER_18] =

_R("RTL8168cp/8111cp", RTL_TD_1, NULL, JUMBO_6K, false),

[RTL_GIGA_MAC_VER_19] =

_R("RTL8168c/8111c", RTL_TD_1, NULL, JUMBO_6K, false),

[RTL_GIGA_MAC_VER_20] =

_R("RTL8168c/8111c", RTL_TD_1, NULL, JUMBO_6K, false),

[RTL_GIGA_MAC_VER_21] =

_R("RTL8168c/8111c", RTL_TD_1, NULL, JUMBO_6K, false),

[RTL_GIGA_MAC_VER_22] =

_R("RTL8168c/8111c", RTL_TD_1, NULL, JUMBO_6K, false),

[RTL_GIGA_MAC_VER_23] =

_R("RTL8168cp/8111cp", RTL_TD_1, NULL, JUMBO_6K, false),

[RTL_GIGA_MAC_VER_24] =

_R("RTL8168cp/8111cp", RTL_TD_1, NULL, JUMBO_6K, false),

[RTL_GIGA_MAC_VER_25] =

_R("RTL8168d/8111d", RTL_TD_1, FIRMWARE_8168D_1,

JUMBO_9K, false),

[RTL_GIGA_MAC_VER_26] =

_R("RTL8168d/8111d", RTL_TD_1, FIRMWARE_8168D_2,

JUMBO_9K, false),

[RTL_GIGA_MAC_VER_27] =

_R("RTL8168dp/8111dp", RTL_TD_1, NULL, JUMBO_9K, false),

[RTL_GIGA_MAC_VER_28] =

_R("RTL8168dp/8111dp", RTL_TD_1, NULL, JUMBO_9K, false),

[RTL_GIGA_MAC_VER_29] =

_R("RTL8105e", RTL_TD_1, FIRMWARE_8105E_1,

JUMBO_1K, true),

[RTL_GIGA_MAC_VER_30] =

_R("RTL8105e", RTL_TD_1, FIRMWARE_8105E_1,

JUMBO_1K, true),

[RTL_GIGA_MAC_VER_31] =

_R("RTL8168dp/8111dp", RTL_TD_1, NULL, JUMBO_9K, false),

[RTL_GIGA_MAC_VER_32] =

_R("RTL8168e/8111e", RTL_TD_1, FIRMWARE_8168E_1,

JUMBO_9K, false),

[RTL_GIGA_MAC_VER_33] =

_R("RTL8168e/8111e", RTL_TD_1, FIRMWARE_8168E_2,

JUMBO_9K, false),

[RTL_GIGA_MAC_VER_34] =

_R("RTL8168evl/8111evl",RTL_TD_1, FIRMWARE_8168E_3,

JUMBO_9K, false),

[RTL_GIGA_MAC_VER_35] =

_R("RTL8168f/8111f", RTL_TD_1, FIRMWARE_8168F_1,

JUMBO_9K, false),

[RTL_GIGA_MAC_VER_36] =

_R("RTL8168f/8111f", RTL_TD_1, FIRMWARE_8168F_2,

JUMBO_9K, false),

[RTL_GIGA_MAC_VER_37] =

_R("RTL8402", RTL_TD_1, FIRMWARE_8402_1,

JUMBO_1K, true),

[RTL_GIGA_MAC_VER_38] =

_R("RTL8411", RTL_TD_1, FIRMWARE_8411_1,

JUMBO_9K, false),

[RTL_GIGA_MAC_VER_39] =

_R("RTL8106e", RTL_TD_1, FIRMWARE_8106E_1,

JUMBO_1K, true),

[RTL_GIGA_MAC_VER_40] =

_R("RTL8168g/8111g", RTL_TD_1, FIRMWARE_8168G_2,

JUMBO_9K, false),

[RTL_GIGA_MAC_VER_41] =

_R("RTL8168g/8111g", RTL_TD_1, NULL, JUMBO_9K, false),

[RTL_GIGA_MAC_VER_42] =

_R("RTL8168g/8111g", RTL_TD_1, FIRMWARE_8168G_3,

JUMBO_9K, false),

[RTL_GIGA_MAC_VER_43] =

_R("RTL8106e", RTL_TD_1, FIRMWARE_8106E_2,

JUMBO_1K, true),

[RTL_GIGA_MAC_VER_44] =

_R("RTL8411", RTL_TD_1, FIRMWARE_8411_2,

JUMBO_9K, false),

};

#undef _R

enum cfg_version {

RTL_CFG_0 = 0x00,

RTL_CFG_1,

RTL_CFG_2

};

static DEFINE_PCI_DEVICE_TABLE(rtl8169_pci_tbl) = {

{ PCI_DEVICE(PCI_VENDOR_ID_REALTEK, 0x8129), 0, 0, RTL_CFG_0 },

{ PCI_DEVICE(PCI_VENDOR_ID_REALTEK, 0x8136), 0, 0, RTL_CFG_2 },

{ PCI_DEVICE(PCI_VENDOR_ID_REALTEK, 0x8167), 0, 0, RTL_CFG_0 },

{ PCI_DEVICE(PCI_VENDOR_ID_REALTEK, 0x8168), 0, 0, RTL_CFG_1 },

{ PCI_DEVICE(PCI_VENDOR_ID_REALTEK, 0x8169), 0, 0, RTL_CFG_0 },

{ PCI_VENDOR_ID_DLINK, 0x4300,

PCI_VENDOR_ID_DLINK, 0x4b10, 0, 0, RTL_CFG_1 },

{ PCI_DEVICE(PCI_VENDOR_ID_DLINK, 0x4300), 0, 0, RTL_CFG_0 },

{ PCI_DEVICE(PCI_VENDOR_ID_DLINK, 0x4302), 0, 0, RTL_CFG_0 },

{ PCI_DEVICE(PCI_VENDOR_ID_AT, 0xc107), 0, 0, RTL_CFG_0 },

{ PCI_DEVICE(0x16ec, 0x0116), 0, 0, RTL_CFG_0 },

{ PCI_VENDOR_ID_LINKSYS, 0x1032,

PCI_ANY_ID, 0x0024, 0, 0, RTL_CFG_0 },

{ 0x0001, 0x8168,

PCI_ANY_ID, 0x2410, 0, 0, RTL_CFG_2 },

{0,},

};

MODULE_DEVICE_TABLE(pci, rtl8169_pci_tbl);

static int rx_buf_sz = 16383;

static int use_dac;

static struct {

u32 msg_enable;

} debug = { -1 };

enum rtl_registers {

MAC0 = 0, /* Ethernet hardware address. */

MAC4 = 4,

MAR0 = 8, /* Multicast filter. */

CounterAddrLow = 0x10,

CounterAddrHigh = 0x14,

TxDescStartAddrLow = 0x20,

TxDescStartAddrHigh = 0x24,

TxHDescStartAddrLow = 0x28,

TxHDescStartAddrHigh = 0x2c,

FLASH = 0x30,

ERSR = 0x36,

ChipCmd = 0x37,

TxPoll = 0x38,

IntrMask = 0x3c,

IntrStatus = 0x3e,

TxConfig = 0x40,

#define TXCFG_AUTO_FIFO (1 << 7) /* 8111e-vl */

#define TXCFG_EMPTY (1 << 11) /* 8111e-vl */

RxConfig = 0x44,

#define RX128_INT_EN (1 << 15) /* 8111c and later */

#define RX_MULTI_EN (1 << 14) /* 8111c only */

#define RXCFG_FIFO_SHIFT 13

/* No threshold before first PCI xfer */

#define RX_FIFO_THRESH (7 << RXCFG_FIFO_SHIFT)

#define RX_EARLY_OFF (1 << 11)

#define RXCFG_DMA_SHIFT 8

/* Unlimited maximum PCI burst. */

#define RX_DMA_BURST (7 << RXCFG_DMA_SHIFT)

RxMissed = 0x4c,

Cfg9346 = 0x50,

Config0 = 0x51,

Config1 = 0x52,

Config2 = 0x53,

#define PME_SIGNAL (1 << 5) /* 8168c and later */

Config3 = 0x54,

Config4 = 0x55,

Config5 = 0x56,

MultiIntr = 0x5c,

PHYAR = 0x60,

PHYstatus = 0x6c,

RxMaxSize = 0xda,

CPlusCmd = 0xe0,

IntrMitigate = 0xe2,

RxDescAddrLow = 0xe4,

RxDescAddrHigh = 0xe8,

EarlyTxThres = 0xec, /* 8169. Unit of 32 bytes. */

#define NoEarlyTx 0x3f /* Max value : no early transmit. */

MaxTxPacketSize = 0xec, /* 8101/8168. Unit of 128 bytes. */

#define TxPacketMax (8064 >> 7)

#define EarlySize 0x27

FuncEvent = 0xf0,

FuncEventMask = 0xf4,

FuncPresetState = 0xf8,

FuncForceEvent = 0xfc,

};

enum rtl8110_registers {

TBICSR = 0x64,

TBI_ANAR = 0x68,

TBI_LPAR = 0x6a,

};

enum rtl8168_8101_registers {

CSIDR = 0x64,

CSIAR = 0x68,

#define CSIAR_FLAG 0x80000000

#define CSIAR_WRITE_CMD 0x80000000

#define CSIAR_BYTE_ENABLE 0x0f

#define CSIAR_BYTE_ENABLE_SHIFT 12

#define CSIAR_ADDR_MASK 0x0fff

#define CSIAR_FUNC_CARD 0x00000000

#define CSIAR_FUNC_SDIO 0x00010000

#define CSIAR_FUNC_NIC 0x00020000

#define CSIAR_FUNC_NIC2 0x00010000

PMCH = 0x6f,

EPHYAR = 0x80,

#define EPHYAR_FLAG 0x80000000

#define EPHYAR_WRITE_CMD 0x80000000

#define EPHYAR_REG_MASK 0x1f

#define EPHYAR_REG_SHIFT 16

#define EPHYAR_DATA_MASK 0xffff

DLLPR = 0xd0,

#define PFM_EN (1 << 6)

DBG_REG = 0xd1,

#define FIX_NAK_1 (1 << 4)

#define FIX_NAK_2 (1 << 3)

TWSI = 0xd2,

MCU = 0xd3,

#define NOW_IS_OOB (1 << 7)

#define TX_EMPTY (1 << 5)

#define RX_EMPTY (1 << 4)

#define RXTX_EMPTY (TX_EMPTY | RX_EMPTY)

#define EN_NDP (1 << 3)

#define EN_OOB_RESET (1 << 2)

#define LINK_LIST_RDY (1 << 1)

EFUSEAR = 0xdc,

#define EFUSEAR_FLAG 0x80000000

#define EFUSEAR_WRITE_CMD 0x80000000

#define EFUSEAR_READ_CMD 0x00000000

#define EFUSEAR_REG_MASK 0x03ff

#define EFUSEAR_REG_SHIFT 8

#define EFUSEAR_DATA_MASK 0xff

};

enum rtl8168_registers {

LED_FREQ = 0x1a,

EEE_LED = 0x1b,

ERIDR = 0x70,

ERIAR = 0x74,

#define ERIAR_FLAG 0x80000000

#define ERIAR_WRITE_CMD 0x80000000

#define ERIAR_READ_CMD 0x00000000

#define ERIAR_ADDR_BYTE_ALIGN 4

#define ERIAR_TYPE_SHIFT 16

#define ERIAR_EXGMAC (0x00 << ERIAR_TYPE_SHIFT)

#define ERIAR_MSIX (0x01 << ERIAR_TYPE_SHIFT)

#define ERIAR_ASF (0x02 << ERIAR_TYPE_SHIFT)

#define ERIAR_MASK_SHIFT 12

#define ERIAR_MASK_0001 (0x1 << ERIAR_MASK_SHIFT)

#define ERIAR_MASK_0011 (0x3 << ERIAR_MASK_SHIFT)

#define ERIAR_MASK_0101 (0x5 << ERIAR_MASK_SHIFT)

#define ERIAR_MASK_1111 (0xf << ERIAR_MASK_SHIFT)

EPHY_RXER_NUM = 0x7c,

OCPDR = 0xb0, /* OCP GPHY access */

#define OCPDR_WRITE_CMD 0x80000000

#define OCPDR_READ_CMD 0x00000000

#define OCPDR_REG_MASK 0x7f

#define OCPDR_GPHY_REG_SHIFT 16

#define OCPDR_DATA_MASK 0xffff

OCPAR = 0xb4,

#define OCPAR_FLAG 0x80000000

#define OCPAR_GPHY_WRITE_CMD 0x8000f060

#define OCPAR_GPHY_READ_CMD 0x0000f060

GPHY_OCP = 0xb8,

RDSAR1 = 0xd0, /* 8168c only. Undocumented on 8168dp */

MISC = 0xf0, /* 8168e only. */

#define TXPLA_RST (1 << 29)

#define DISABLE_LAN_EN (1 << 23) /* Enable GPIO pin */

#define PWM_EN (1 << 22)

#define RXDV_GATED_EN (1 << 19)

#define EARLY_TALLY_EN (1 << 16)

};

enum rtl_register_content {

/* InterruptStatusBits */

SYSErr = 0x8000,

PCSTimeout = 0x4000,

SWInt = 0x0100,

TxDescUnavail = 0x0080,

RxFIFOOver = 0x0040,

LinkChg = 0x0020,

RxOverflow = 0x0010,

TxErr = 0x0008,

TxOK = 0x0004,

RxErr = 0x0002,

RxOK = 0x0001,

/* RxStatusDesc */

RxBOVF = (1 << 24),

RxFOVF = (1 << 23),

RxRWT = (1 << 22),

RxRES = (1 << 21),

RxRUNT = (1 << 20),

RxCRC = (1 << 19),

/* ChipCmdBits */

StopReq = 0x80,

CmdReset = 0x10,

CmdRxEnb = 0x08,

CmdTxEnb = 0x04,

RxBufEmpty = 0x01,

/* TXPoll register p.5 */

HPQ = 0x80, /* Poll cmd on the high prio queue */

NPQ = 0x40, /* Poll cmd on the low prio queue */

FSWInt = 0x01, /* Forced software interrupt */

/* Cfg9346Bits */

Cfg9346_Lock = 0x00,

Cfg9346_Unlock = 0xc0,

/* rx_mode_bits */

AcceptErr = 0x20,

AcceptRunt = 0x10,

AcceptBroadcast = 0x08,

AcceptMulticast = 0x04,

AcceptMyPhys = 0x02,