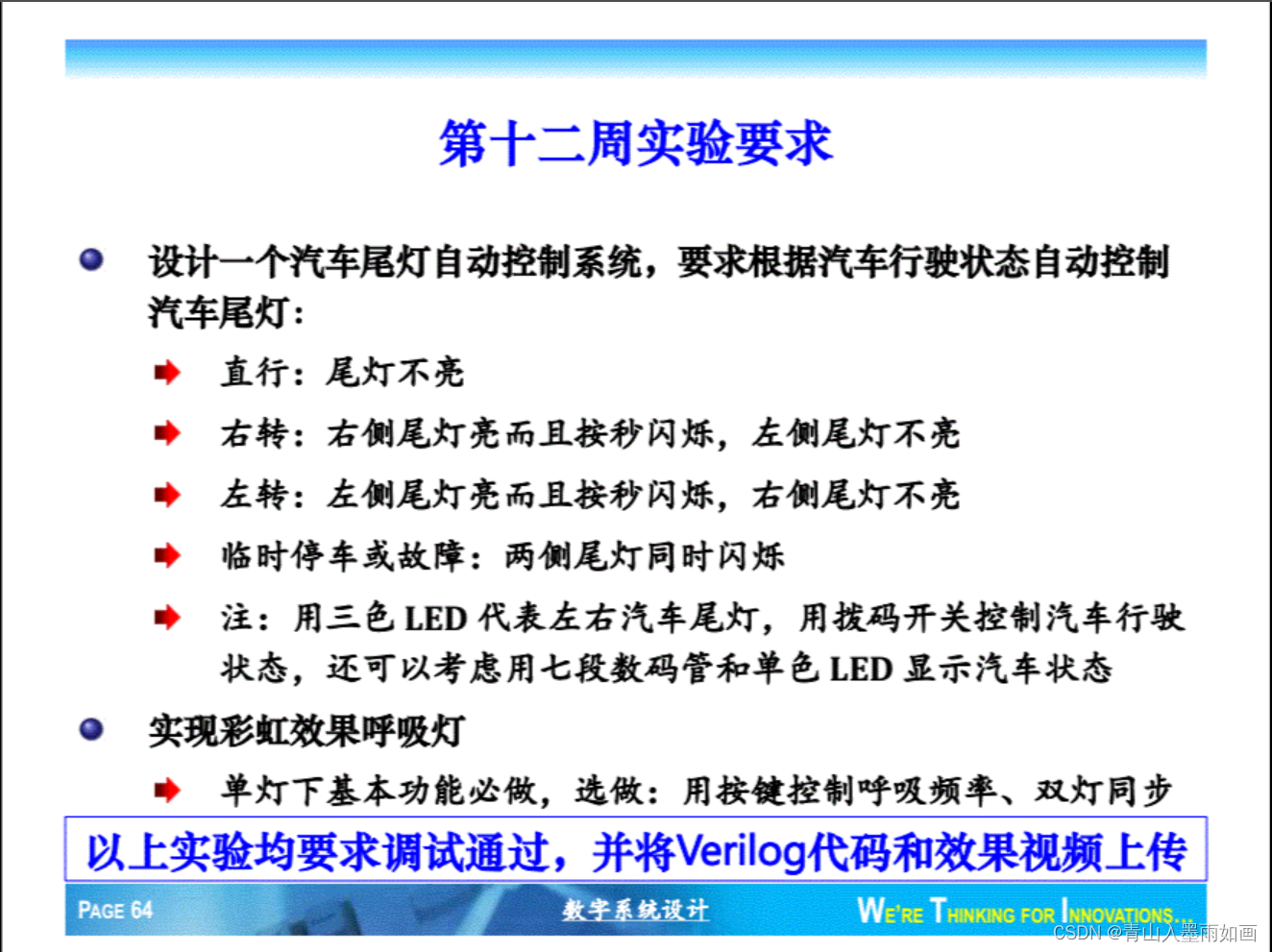

本文介绍: 设计一个汽车尾灯自动控制系统,要求根据汽车行驶状态自动控制汽车尾灯:直行:尾灯不亮;右转:右侧尾灯亮而且按秒闪烁,左侧尾灯不亮;左转:左侧尾灯亮而且按秒闪烁,右侧尾灯不亮;临时停车或者故障:两侧尾灯同时闪烁;注:用三色LED代码表左右汽车尾灯,用拨码开关控制汽车行驶状态没还可以考虑用七段数码管和单色LED显示汽车的状态。

北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客

一.题目要求

二.代码部分

2.1 car_system.v

2.2 divide.v

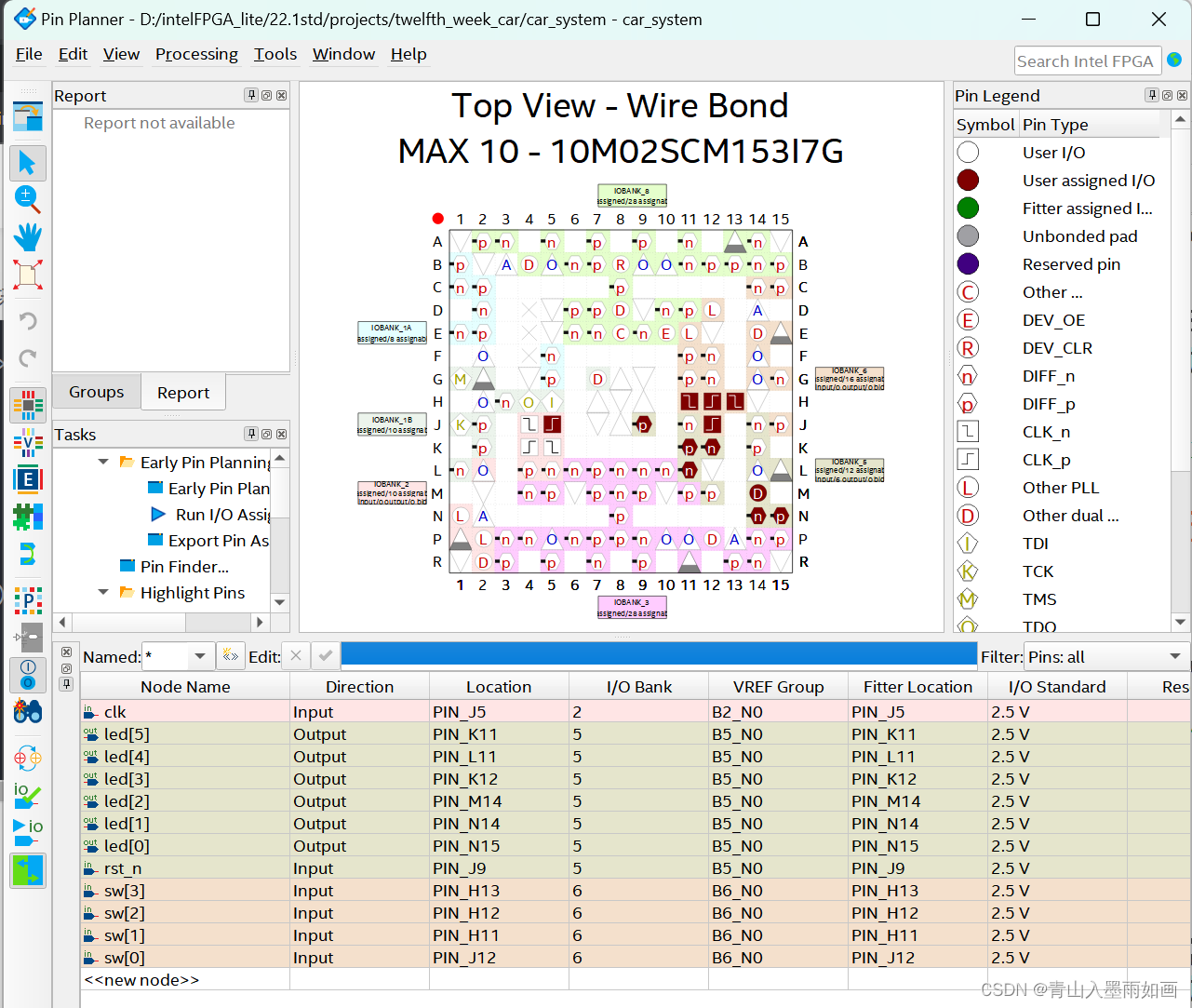

三.管脚分配

四.实现效果

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。

![[软件工具]文档页数统计工具软件pdf统计页数word统计页数ppt统计页数图文打印店快速报价工具](https://img-blog.csdnimg.cn/direct/09dfbaff3e9a47a9a551dd65fef5d482.jpeg)