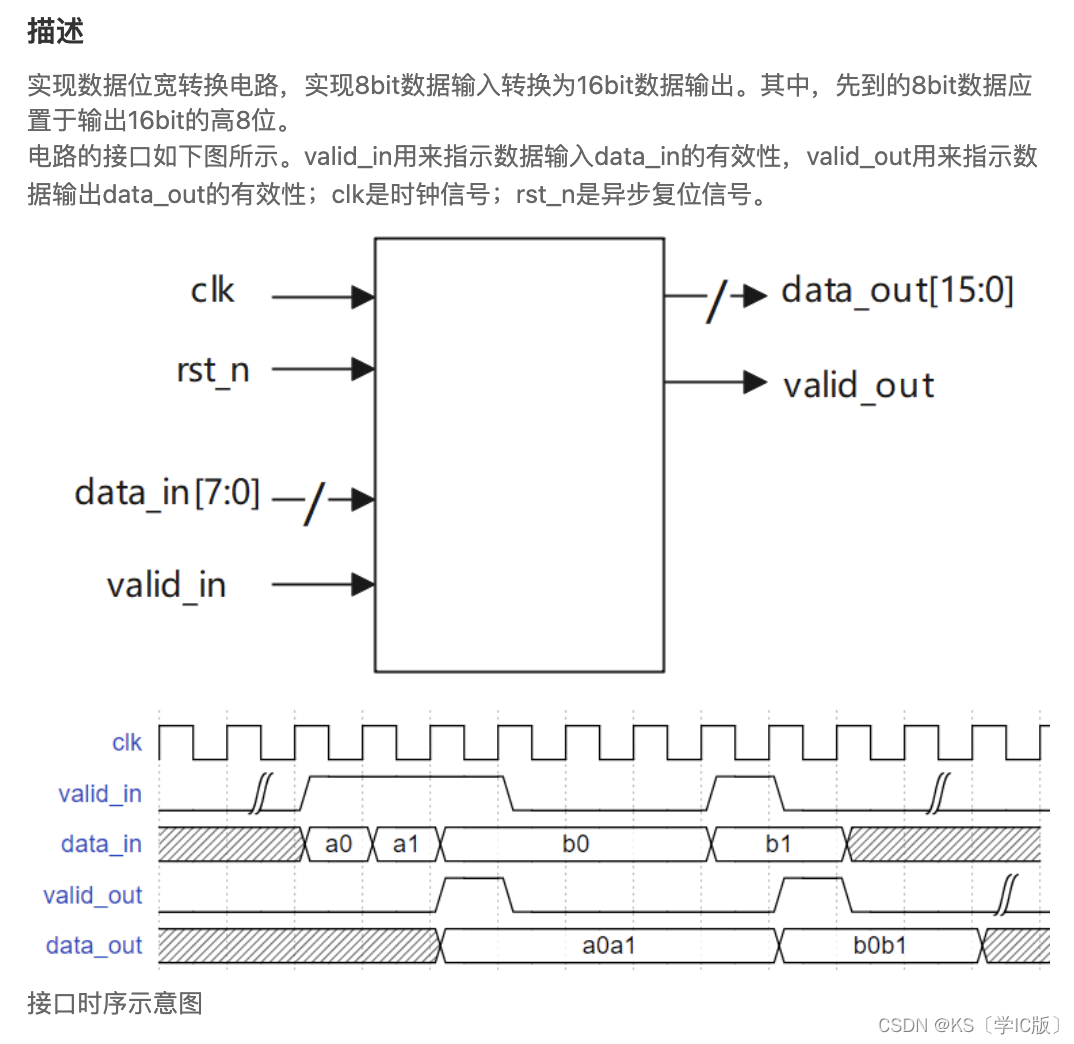

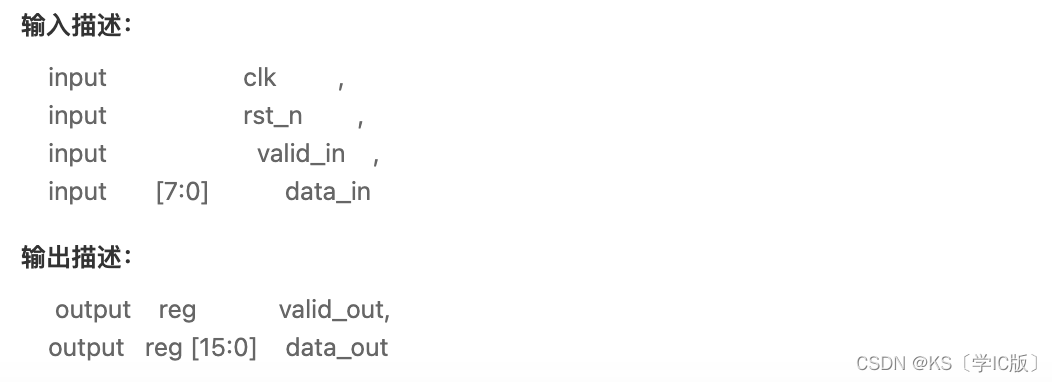

本文介绍: 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网根据时序图,数据是在第二个数据到来之后输出,当仅有一个数据到来时,不产生输出,所以内部需要一个指示信号valid_cnt,用来指示数据缓存状态。当data_lock内已缓存第一个数据时,valid_cnt拉高,当第二个数据到来后valid_cnt拉低endendendendendmodule。

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。