北邮22级信通院数电实验_青山如墨雨如画的博客-CSDN博客

一.代码部分

1.1 counter_24.v

module counter_24

(

input clk,rst,hold,

output [8:0] seg_led_1,

output [8:0] seg_led_2,

output reg [7:0] led

);

wire clk_lh;

wire hold_pulse;

reg hold_flag;

reg back_to_zero_flag;

reg [6:0] seg [16:0];

reg [3:0] cnt_ge;

reg [3:0] cnt_shi;

initial

begin

seg[0] = 7'h3f;

seg[1] = 7'h06;

seg[2] = 7'h5b;

seg[3] = 7'h4f;

seg[4] = 7'h66;

seg[5] = 7'h6d;

seg[6] = 7'h7d;

seg[7] = 7'h07;

seg[8] = 7'h7f;

seg[9] = 7'h6f;

seg[10] = 7'hf7;

seg[11] = 7'h7c;

seg[12] = 7'h39;

seg[13] = 7'h5e;

seg[14] = 7'h79;

seg[15] = 7'h71;

end

debounce debounce_1

(

.clk(clk),

.rst(rst),

.key(hold),

.key_pulse(hold_pulse)

);

divide # (.WIDTH(32),.N(12000000)) divide_1

(

.clk(clk),

.rst_n(rst),

.clkout(clk_lh)

);

always @ (posedge hold_pulse)

if(!rst==1)

hold_flag <= 0;

else

hold_flag <= ~hold_flag;

always @ (*)

if(!rst==1)

back_to_zero_flag <= 0;

else if( cnt_shi==0 && cnt_ge==0)

back_to_zero_flag <= 1;

else

back_to_zero_flag <= 0;

always @ (posedge clk_lh or negedge rst)

begin

if(!rst==1)

begin

cnt_ge <= 4'd4;

cnt_shi <=4'd2;

end

else if(hold_flag==1)

begin

cnt_ge <= cnt_ge;

cnt_shi <= cnt_shi;

end

else if(cnt_shi==0 && cnt_ge==0)

begin

cnt_shi <= cnt_shi;

cnt_ge <=cnt_ge;

end

else if(cnt_ge==0)

begin

cnt_ge <=4'd9;

cnt_shi <= cnt_shi-1;

end

else

begin cnt_ge <= cnt_ge-1; end

end

//计时完成点亮led

always @ (back_to_zero_flag)

begin

if(back_to_zero_flag == 1)

led = 8'b0;

else

led = 8'b1111_1111;

end

assign seg_led_1[8:0] = {2'b00,seg[cnt_ge]};

assign seg_led_2[8:0] = {2'b00,seg[cnt_shi]};

endmodule

1.2 divide.v

module divide ( clk,rst_n,clkout);

input clk,rst_n; //输入信号,其中clk连接到FPGA的C1脚,频率为12MHz

output clkout; //输出信号,可以连接到LED观察分频的时钟

//parameter是verilog里常数语句

parameter WIDTH = 3; //计数器的位数,计数的最大值为 2**WIDTH-1

parameter N = 5; //分频系数,请确保 N < 2**WIDTH-1,否则计数会溢出

reg [WIDTH-1:0] cnt_p,cnt_n; //cnt_p为上升沿触发时的计数器,cnt_n为下降沿触发时的计数器

reg clk_p,clk_n; //clk_p为上升沿触发时分频时钟,clk_n为下降沿触发时分频时钟

//上升沿触发时计数器的控制

always @ (posedge clk or negedge rst_n ) //posedge和negedge是verilog表示信号上升沿和下降沿

//当clk上升沿来临或者rst_n变低的时候执行一次always里的语句

begin

if(!rst_n)

cnt_p<=0;

else if (cnt_p==(N-1))

cnt_p<=0;

else cnt_p<=cnt_p+1; //计数器一直计数,当计数到N-1的时候清零,这是一个模N的计数器

end

//上升沿触发的分频时钟输出,如果N为奇数得到的时钟占空比不是50%;如果N为偶数得到的时钟占空比为50%

always @ (posedge clk or negedge rst_n)

begin

if(!rst_n)

clk_p<=0;

else if (cnt_p<(N>>1)) //N>>1表示右移一位,相当于除以2去掉余数

clk_p<=0;

else

clk_p<=1; //得到的分频时钟正周期比负周期多一个clk时钟

end

//下降沿触发时计数器的控制

always @ (negedge clk or negedge rst_n)

begin

if(!rst_n)

cnt_n<=0;

else if (cnt_n==(N-1))

cnt_n<=0;

else cnt_n<=cnt_n+1;

end

//下降沿触发的分频时钟输出,和clk_p相差半个时钟

always @ (negedge clk)

begin

if(!rst_n)

clk_n<=0;

else if (cnt_n<(N>>1))

clk_n<=0;

else

clk_n<=1; //得到的分频时钟正周期比负周期多一个clk时钟

end

assign clkout = (N==1)?clk:(N[0])?(clk_p&clk_n):clk_p; //条件判断表达式

//当N=1时,直接输出clk

//当N为偶数也就是N的最低位为0,N(0)=0,输出clk_p

//当N为奇数也就是N最低位为1,N(0)=1,输出clk_p&clk_n。正周期多所以是相与

endmodule 1.3 debounce.v

module debounce (clk,rst,key,key_pulse);

parameter N = 1; //要消除的按键的数量

input clk;

input rst;

input [N-1:0] key; //输入的按键

output [N-1:0] key_pulse; //按键动作产生的脉冲

reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值

reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值

wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲

//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中

always @(posedge clk or negedge rst)

begin

if (!rst) begin

key_rst <= {N{1'b1}}; //初始化时给key_rst赋值全为1,{}中表示N个1

key_rst_pre <= {N{1'b1}};

end

else begin

key_rst <= key; //第一个时钟上升沿触发之后key的值赋给key_rst,

//同时key_rst的值赋给key_rst_pre

key_rst_pre <= key_rst; //非阻塞赋值。

//相当于经过两个时钟触发,

//key_rst存储的是当前时刻key的值,

//key_rst_pre存储的是前一个时钟的key的值

end

end

assign key_edge = key_rst_pre & (~key_rst);//脉冲边沿检测。

//当key检测到下降沿时,

//key_edge产生一个时钟周期的高电平

reg [17:0] cnt; //产生延时所用的计数器,系统时钟12MHz,

//要延时20ms左右时间,至少需要18位计数器

//产生20ms延时,当检测到key_edge有效是计数器清零开始计数

always @(posedge clk or negedge rst)

begin

if(!rst)

cnt <= 18'h0;

else if(key_edge)

cnt <= 18'h0;

else

cnt <= cnt + 1'h1;

end

reg [N-1:0] key_sec_pre; //延时后检测电平寄存器变量

reg [N-1:0] key_sec;

//延时后检测key,如果按键状态变低产生一个时钟的高脉冲。如果按键状态是高的话说明按键无效

always @(posedge clk or negedge rst)

begin

if (!rst)

key_sec <= {N{1'b1}};

else if (cnt==18'h3ffff)

key_sec <= key;

end

always @(posedge clk or negedge rst)

begin

if (!rst)

key_sec_pre <= {N{1'b1}};

else

key_sec_pre <= key_sec;

end

assign key_pulse = key_sec_pre & (~key_sec);

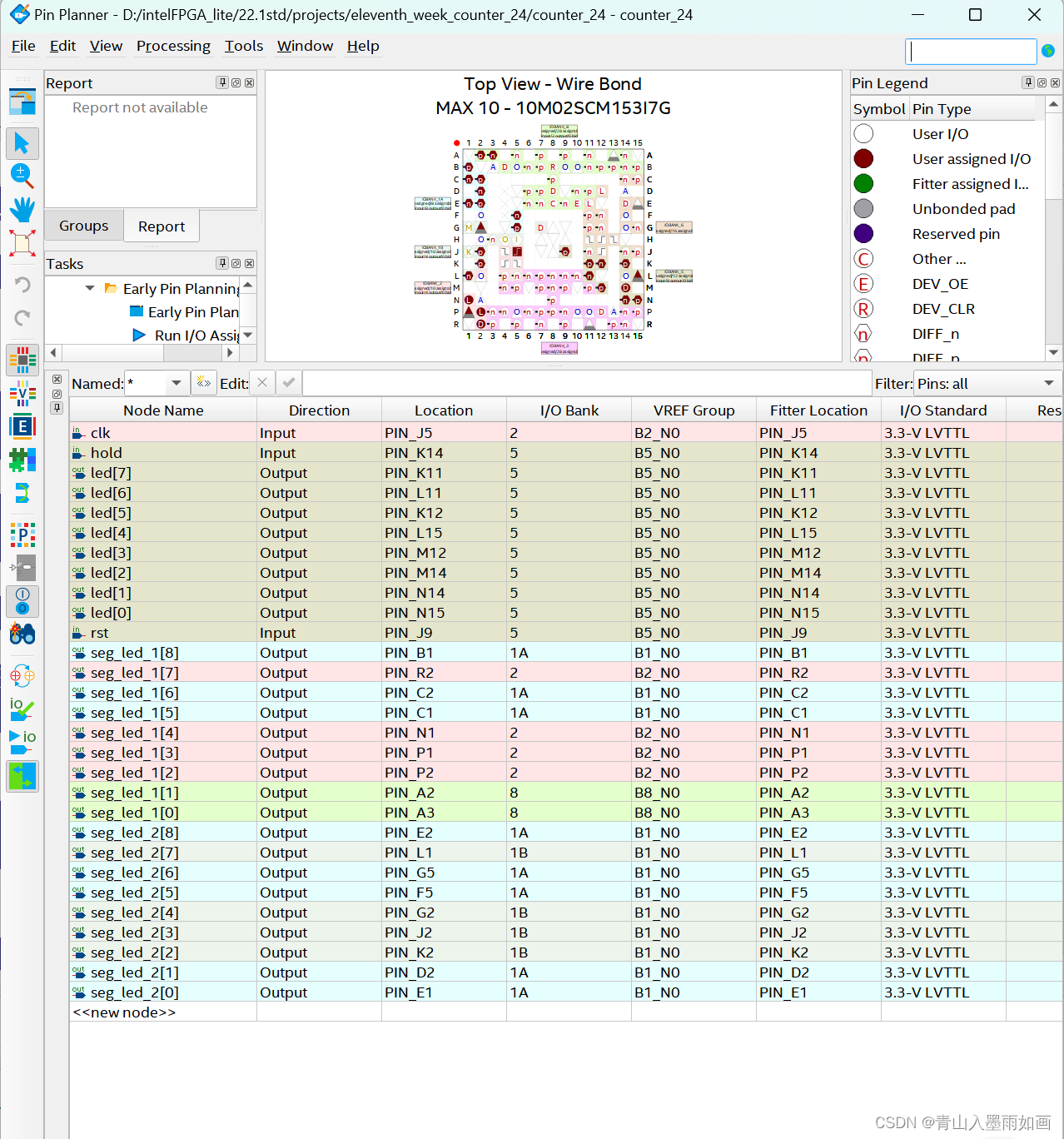

endmodule二.管脚分配

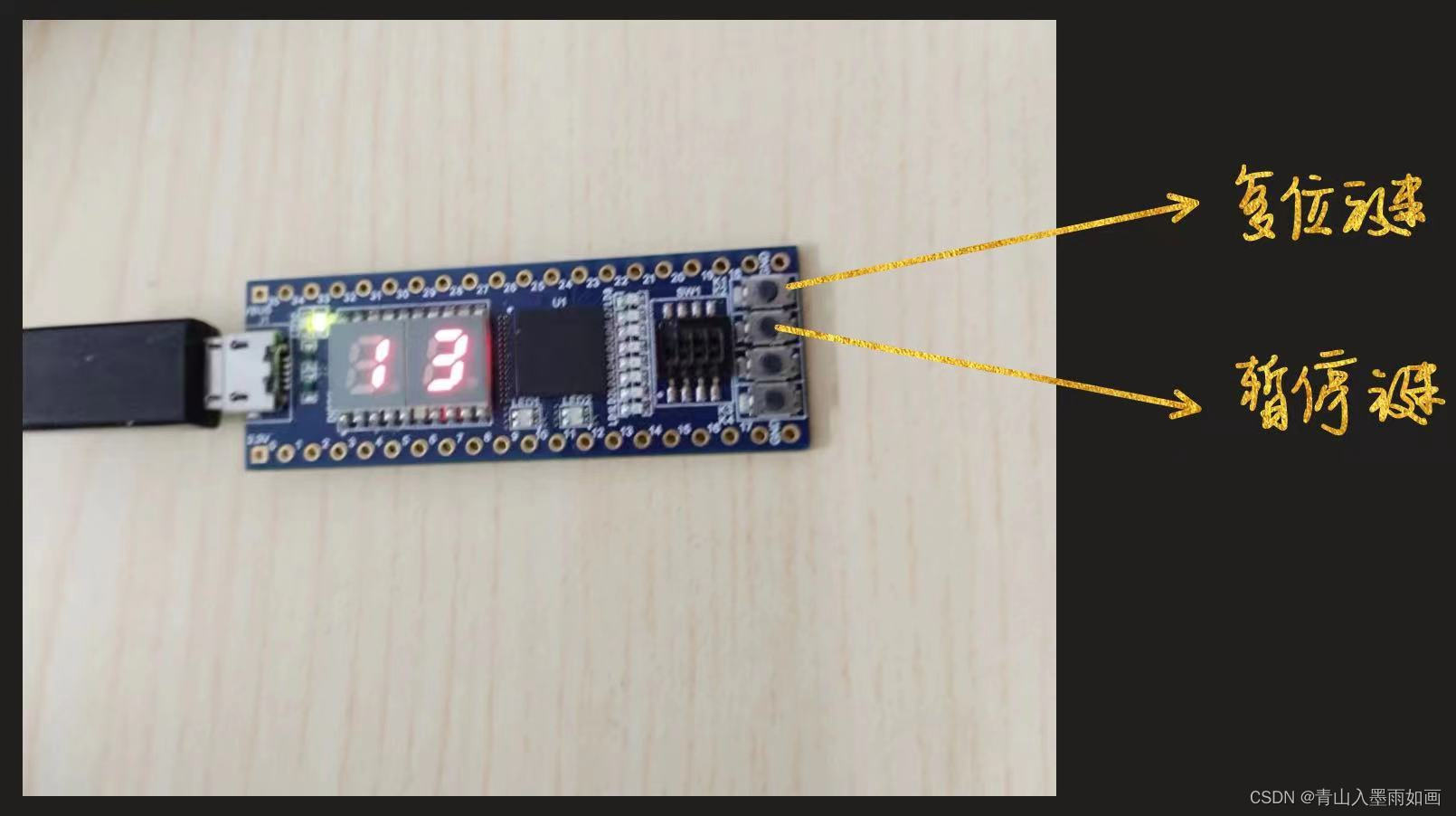

三.实验效果

原文地址:https://blog.csdn.net/bc202205/article/details/134589529

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:http://www.7code.cn/show_25744.html

如若内容造成侵权/违法违规/事实不符,请联系代码007邮箱:suwngjj01@126.com进行投诉反馈,一经查实,立即删除!

主题授权提示:请在后台主题设置-主题授权-激活主题的正版授权,授权购买:RiTheme官网

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。

![[软件工具]文档页数统计工具软件pdf统计页数word统计页数ppt统计页数图文打印店快速报价工具](https://img-blog.csdnimg.cn/direct/09dfbaff3e9a47a9a551dd65fef5d482.jpeg)