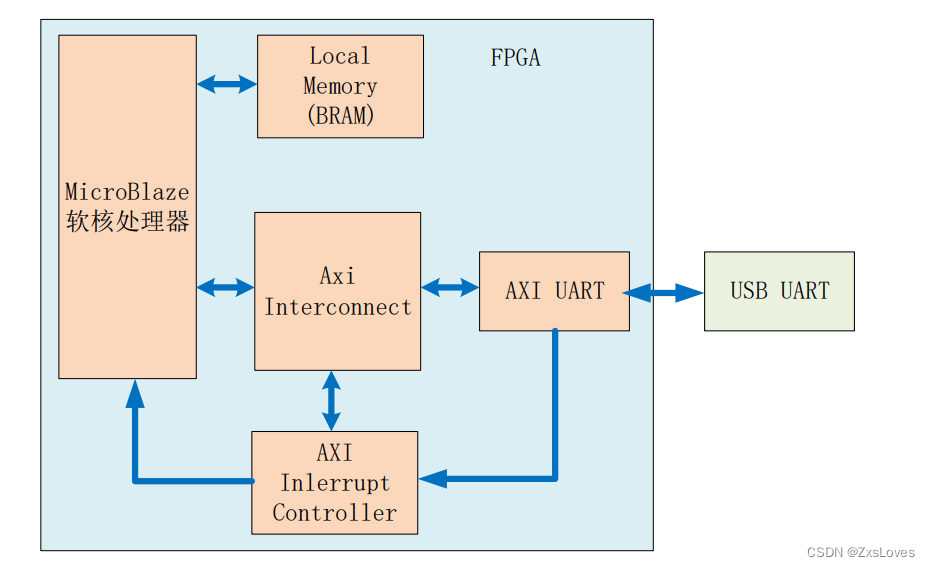

FPGA 之Micro Blaze的串口中断实验

我们在使用 MicroBlaze 进行嵌入式系统设计的时候,通常会用到 AXI Uartlite IP 核与外部设备通信。AXI UART IP 核实现了 RS-232 通讯协议,并使得大家可以设置串口通信相关的波特率、奇偶校验位、停止位和数据位等参数。

AXI UART Lite IP 核具有以下特点:

对通过 axi4-lite 接口接收的字符执行并行到串行转换,并对从串行外围设备接收的字符执行串行到并行转换。

发送和接收 8、7、6 或 5 位字符,有一个停止位,并支持奇数、偶数或无奇偶位的配置。AXI UART Lite可以独立传输和接收数据。

对 通过 axi4-lite 接口接收的字符 执行 并转串 再把 对 外围设备接收的字符执行 串 转 并

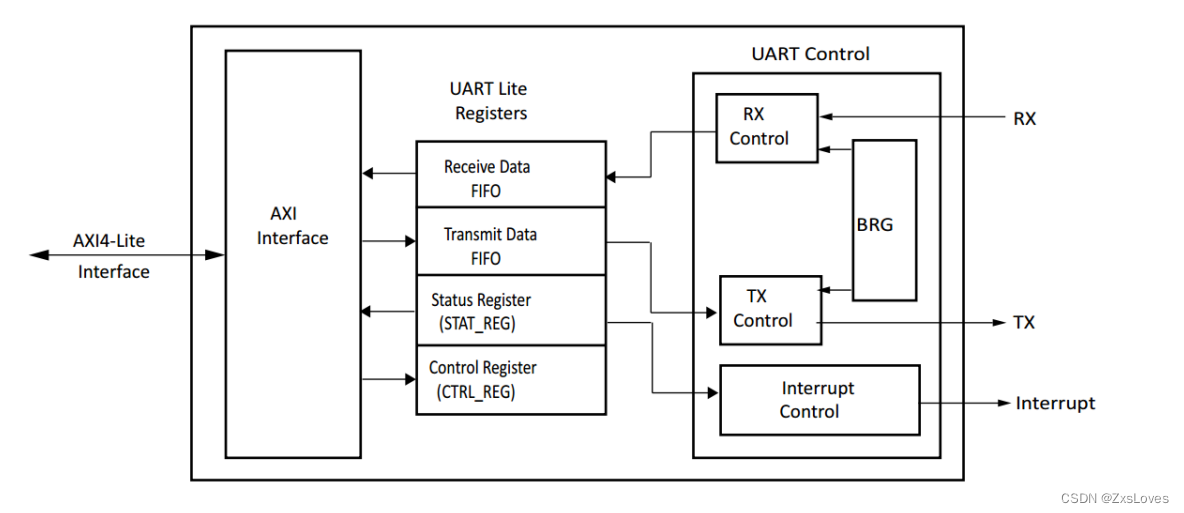

AXI Interface(AXI 接口):该模块实现了用于寄存器访问和数据传输的 AXI4-LITE 从接口。

UART Lite Registers(UART Lite 寄存器模块):此模块包括内存映射寄存器。它由一个控制寄存器、

一个状态寄存器和一对发射/接收 FIFO 组成,两个 FIFO 都有 16 个字符的深度。当接收 FIFO 变为非空或当

发送 FIFO 变为空时,生成上升沿敏感的中断。此中断可以通过使用中断启用/禁用信号来屏蔽。

UART Control(UART 控制模块):该模块包括 Rx Control(接收控制)、Tx Control(发送控制)、

BRG (Baud Rate Generator)和 Interrupt Control(中断控制)四个模块。

AXI UART IP 核提供了 AXI4-Lite 接口,我们可以通过 AXI4-Lite 接口读取状态寄存器或配置 UART Control 模块(复位收发 FIFO、启用中断)。当 AXI UART 接收到上位机发送的数据后,Rx Control 模块根据 BRG 模块产生的波特率将串行的数据转化成并行数据,写入接收 FIFO,然后处理器通过 AXI4-Lite 接口读出接收 FIFO 中的数据;处理器中的数据也可以通过 AXI4-Lite 接口写入发送 FIFO,然后经 Tx Control根据 BRG 模块产生的波特率将并行数据转化为串行数据发送出去。

实验任务 : 是根据 AXI UART IP 核产生的中断信号,完成串口数据的收发。