本文介绍一下常用的存储芯片DDR3,包括DDR3的芯片型号识别、DDR3芯片命名、DDR3的基本结构等知识,为后续掌握FPGA DDR3的读写控制打下坚实基础。

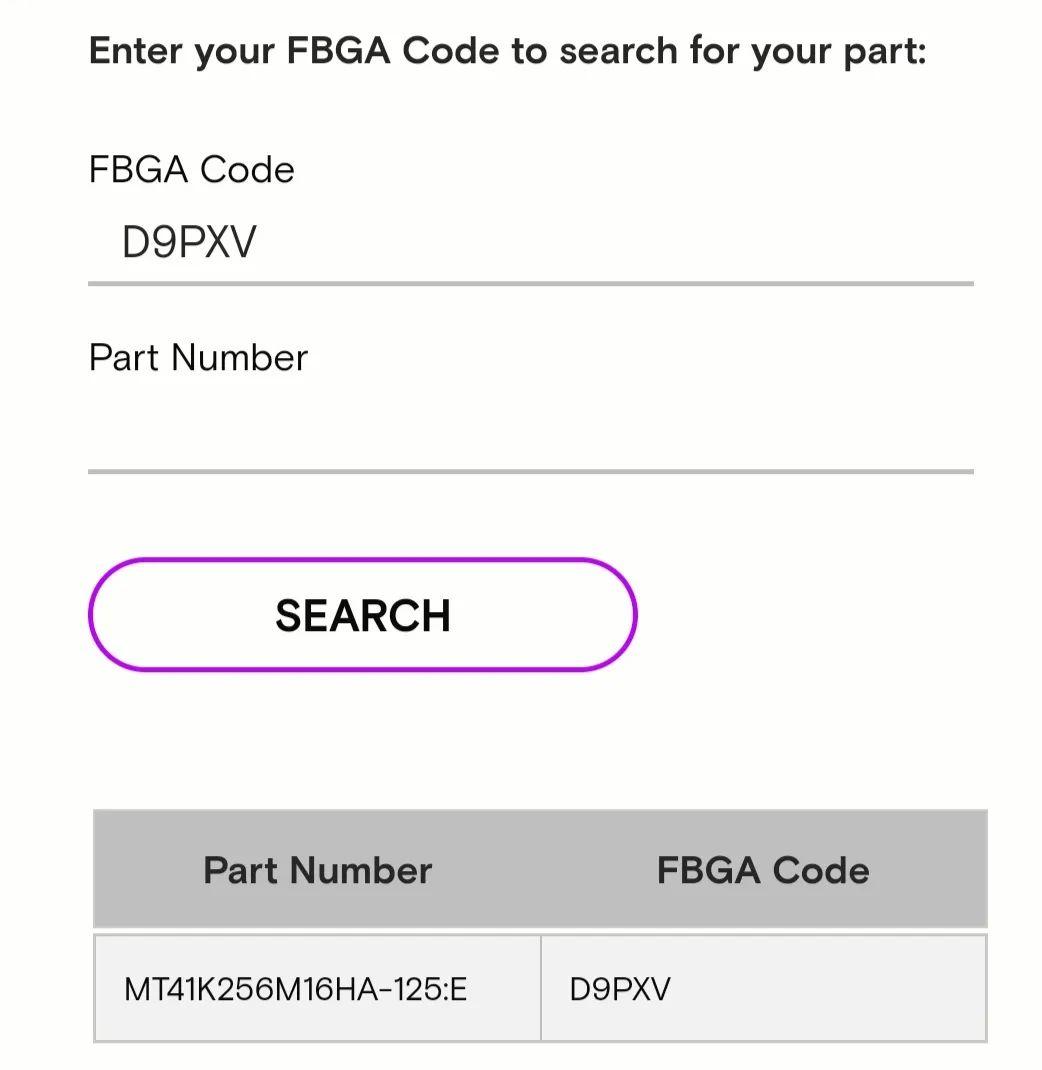

一、DDR3芯片型号

二、DDR3芯片命名

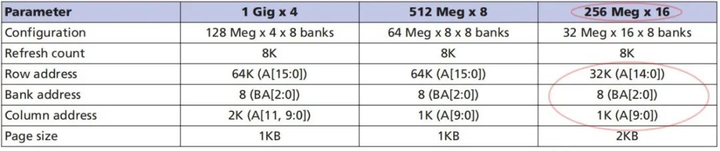

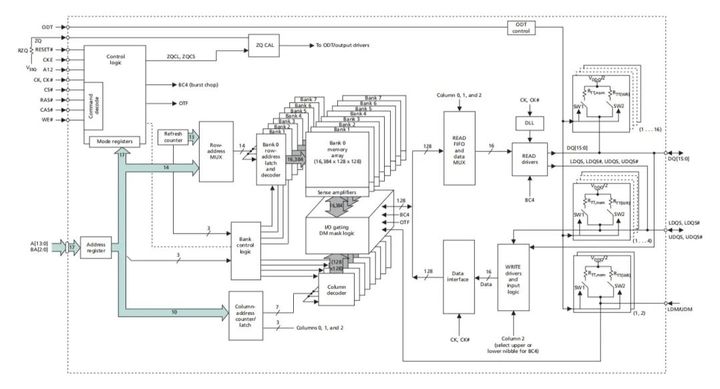

三、DDR3芯片基本结构

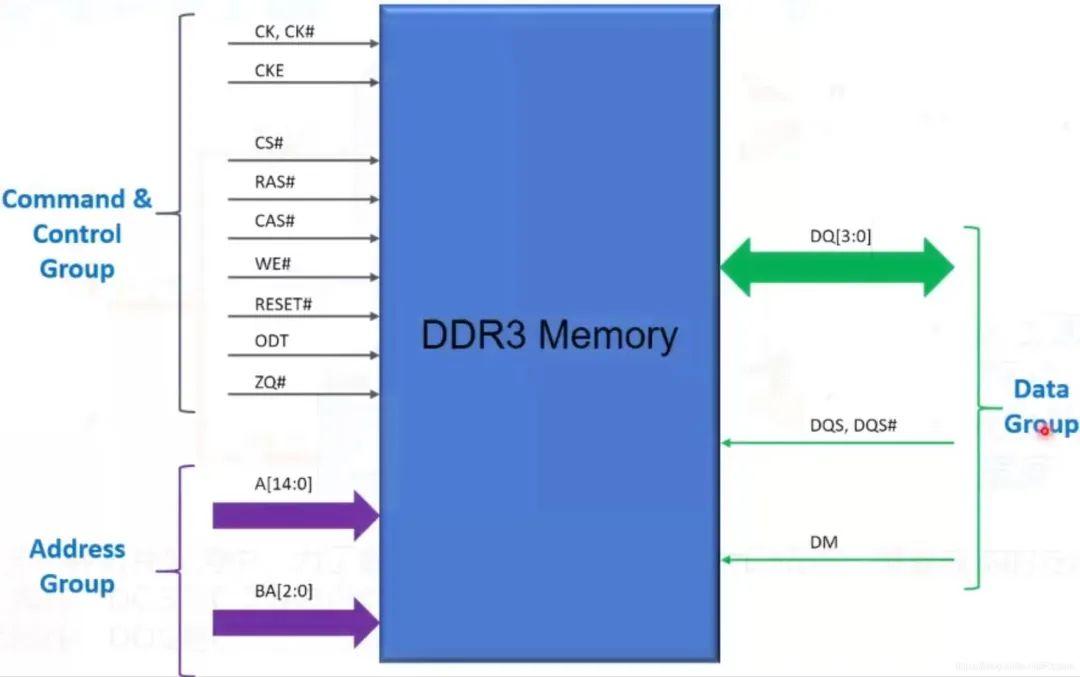

四、DDR 引脚说明

1、控制总总线

2、地址线

3、数据总线

五、DDR关键时间参数

1、传输速率

2、tRCD

3、CL

4、AL

5、tRC

6、tRAS

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。