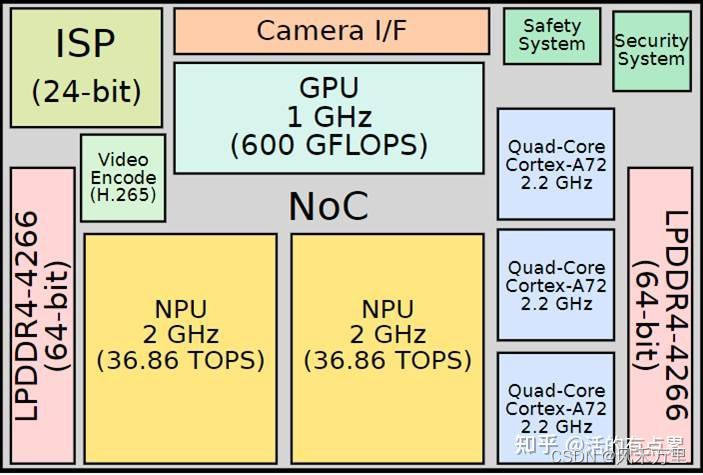

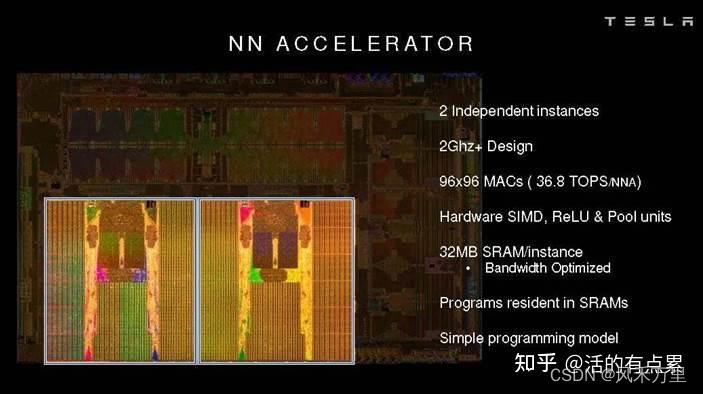

本文介绍: 再后面是已发布的Altan,算力是1000TFLOPS,这次的Thor算力是2000 TOPS强大的着实让人震惊(但是芯片2025才出来,是时间好像有些远的PPT产品)。FSD芯片采用三星(德克萨斯州奥斯汀的工厂)的14纳米工艺技术制造,集成了3个四核Cortex-A72集群,共有12个CPU,工作频率为2.2GHz,1个(ARM的)Mali G71 MP12 GPU,2个NPU工作频率为2GHz,还有其他各种硬件加速器。同时也引入了更复杂的AI模型(NVIDIA大致每2年的产品都会有一个质的提升)。

NVIDIA在9月20日发布的NVIDIA DRIVE Thor 新一代集中式车载计算平台,可在单个安全、可靠的系统上运行高级驾驶员辅助应用和车载信息娱乐应用。提供 2000 万亿次浮点运算性能(2000 万亿次8位浮点运算)。NVIDIA当代产品是Orin,算力是256 TOPS。再后面是已发布的Altan,算力是1000TFLOPS,这次的Thor算力是2000 TOPS强大的着实让人震惊(但是芯片2025才出来,是时间好像有些远的PPT产品)。

先看三个名词解释:

TFLOPS(teraFLOPS)等于每秒一万亿(=10^12)次的浮点运算。FLOPS(Floating–point operations per second的缩写),即每秒浮点运算次数。

TOPS(Tera Operations Per Second的缩写),1TOPS代表处理器每秒钟可进行一万亿次(10^12)操作。

DMIPS:Dhrystone Million Instructions executed Per Second,每秒执行百万条指令,用来计算同一秒内系统的处理能力,即每秒执行了多少百万条指令。

鉴于NVIDIA的Thor还是个PPT,还没有确切产品资料情况下,我们先看下现有芯片的此种算力。特斯拉FSD(自动驾驶的芯片/区别于智能座舱SOC)。

===============================================

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。