本文介绍: 最近收到了一个 Tang nano 9K FPGA开发板,就想借此机会研究一下。官方文档里介绍如果想使用高云的 FPGA,就需要使用 GOWIN IDE,但是需要申请 license 提交一堆资料,我是别人送的就不太方便让别人弄。加上 IDE 其实并不是很适合学习和投入生产,因为 IDE 忽略了很多细节,以及对一些工作做了处理。所以就想找到其他的工作流程,就像可以使用任何文本编辑器加上 Clang/LLVM 就可以编译 C/C++ 程序一样。

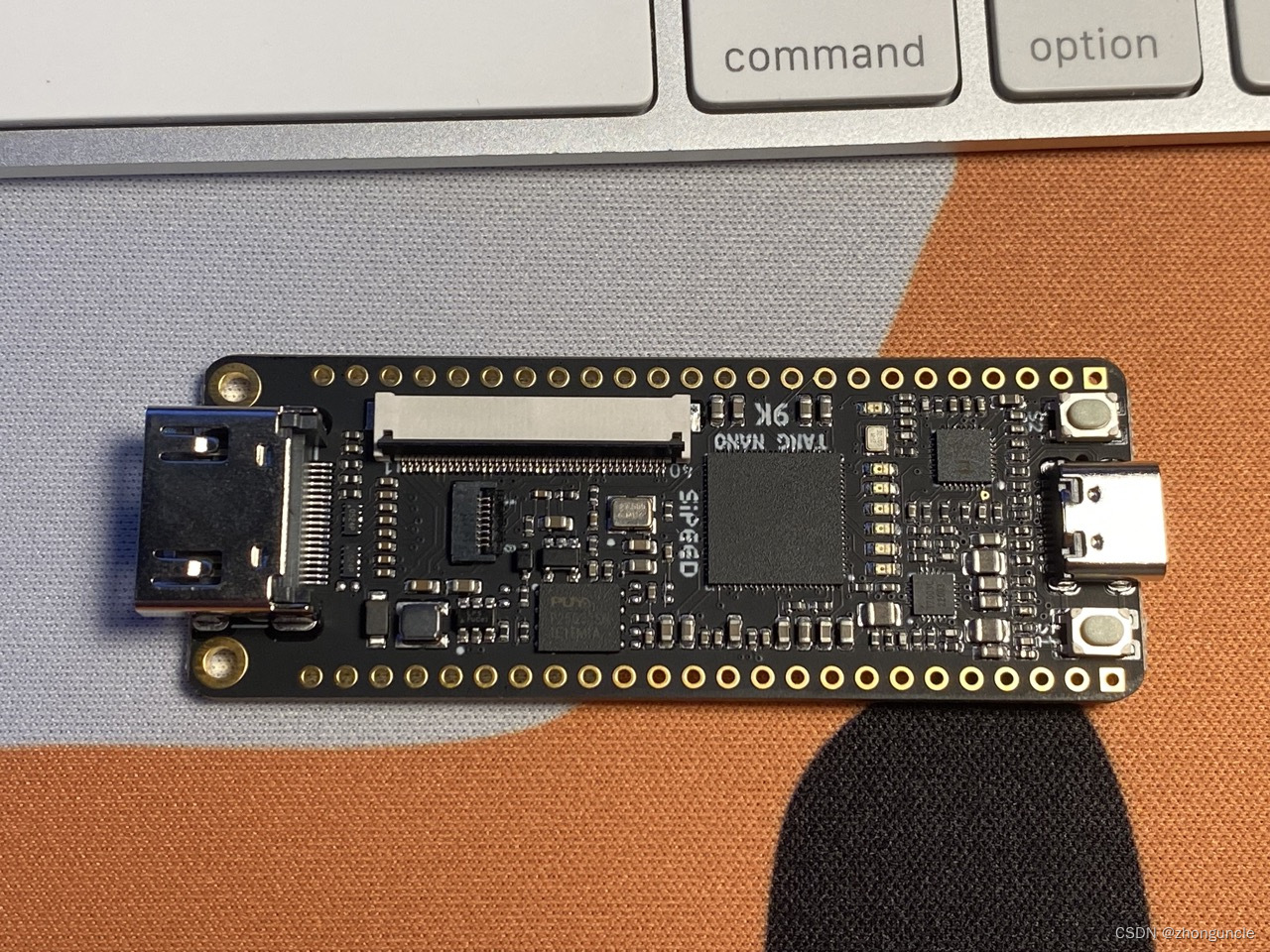

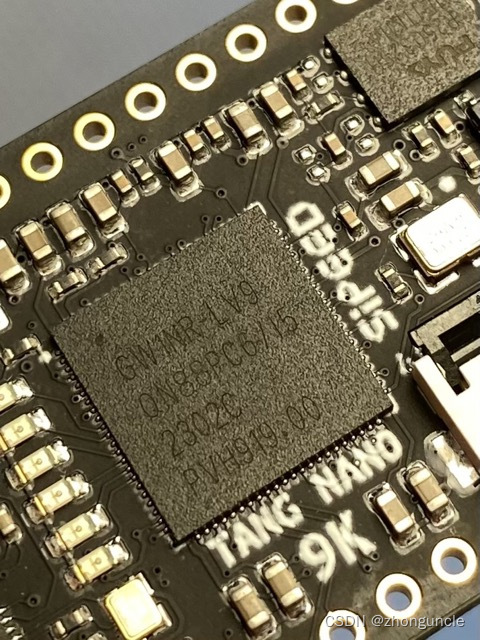

最近收到了一个 Tang nano 9K FPGA开发板,就想借此机会研究一下。

官方文档里介绍如果想使用高云的 FPGA,就需要使用 GOWIN IDE,但是需要申请 license 提交一堆资料,我是别人送的就不太方便让别人弄。加上 IDE 其实并不是很适合学习和投入生产,因为 IDE 忽略了很多细节,以及对一些工作做了处理。所以就想找到其他的工作流程,就像可以使用任何文本编辑器加上 Clang/LLVM 就可以编译 C/C++ 程序一样。

FPGA开发是在开发什么?

首先是需要知道,FPGA 开发到底是在开发什么,这样才能找到需要的工具和软件。

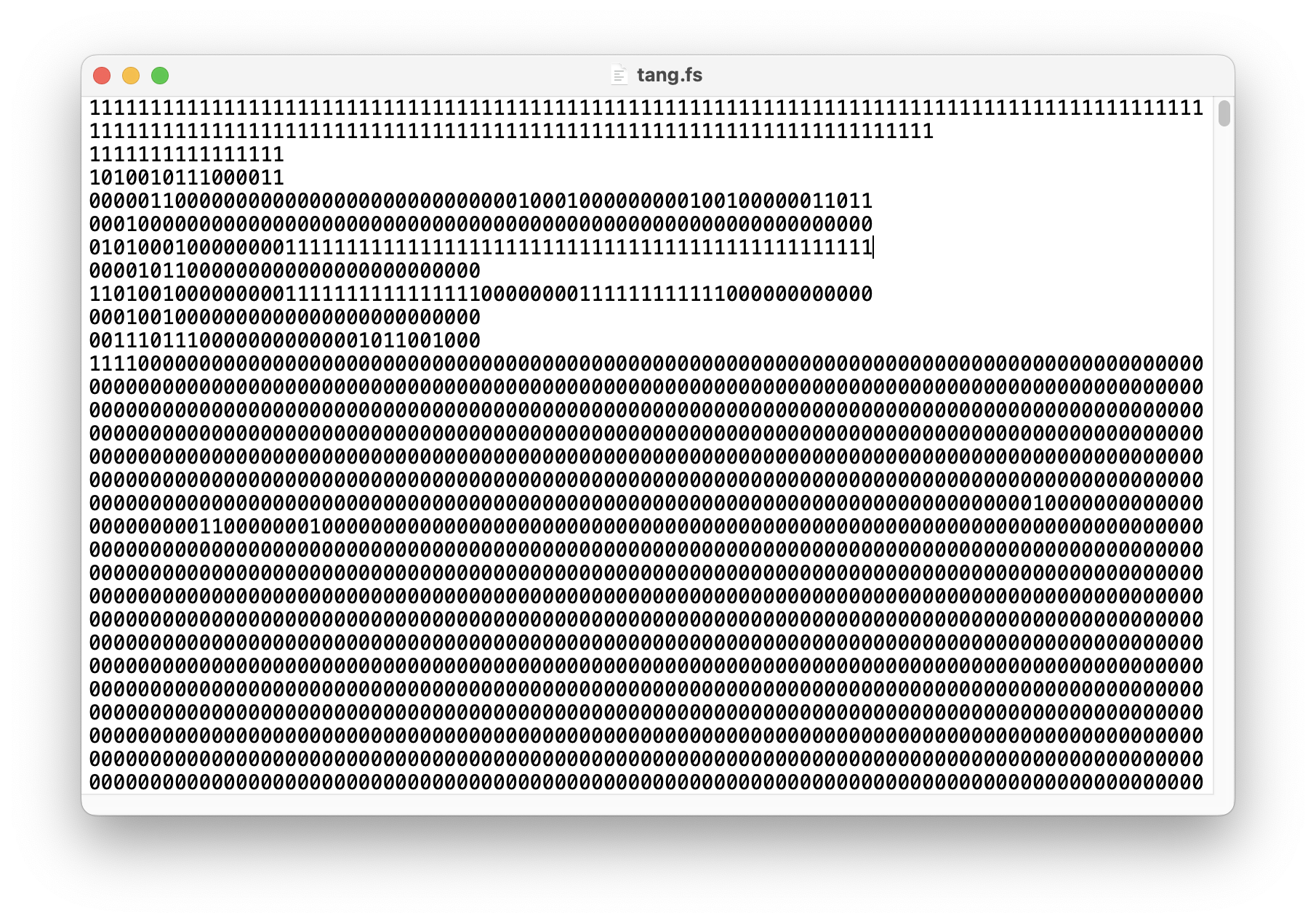

计算机械执行各种指令的本质是给一系列逻辑单元的引脚通电,然后经过逻辑电路之后输出新的电路信号。从软件的层面来说,每个引脚的输入就是一个常见到的一串二进制数字(比如01011101010)中的一位(一般使用的正逻辑中,1表示高电平,0表示低电平),早期的打孔板就是实体版的这种二进制数字。也就是说,最终我们需要的是一个存放二进制指令的文件,然后由 FPGA 执行。

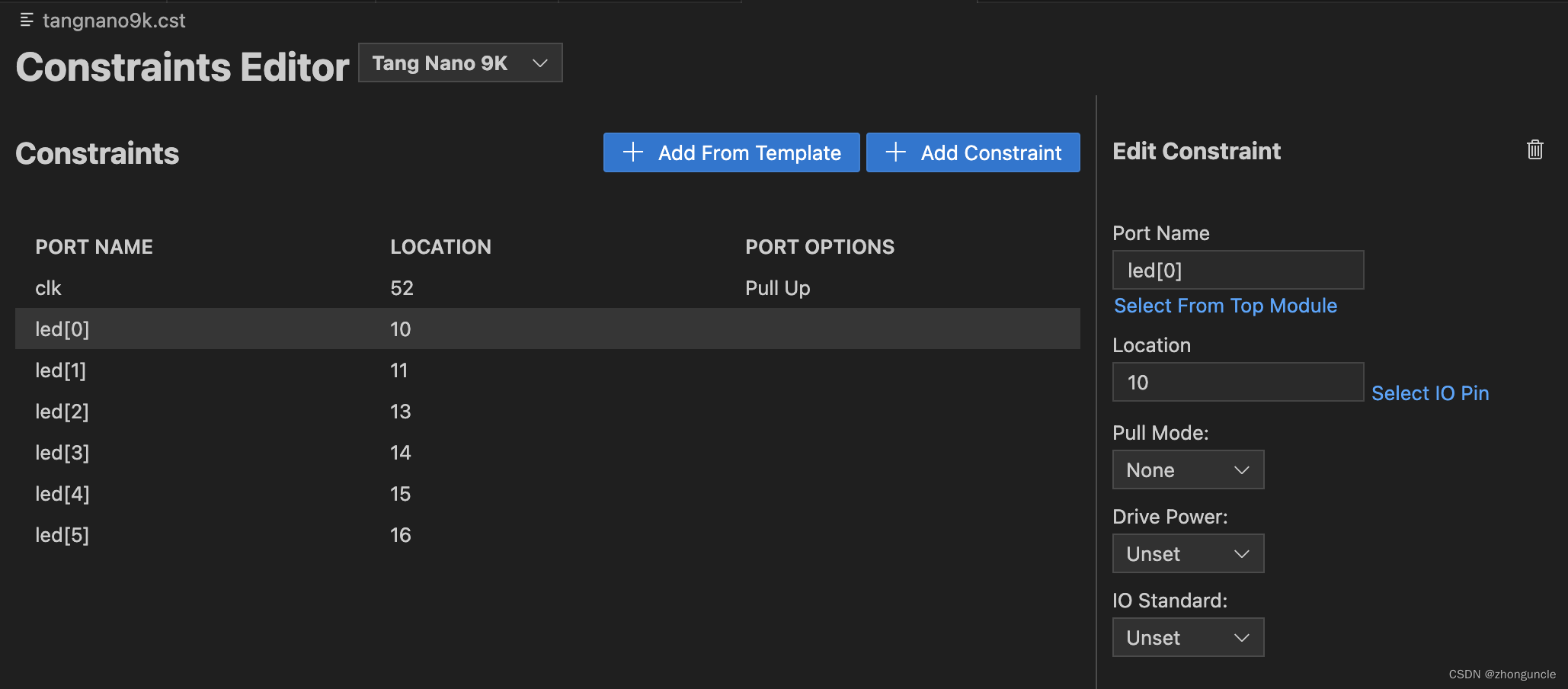

这时候还有一个问题:指令怎么知道接口和针脚谁是谁呢?不知道的话,是没有办法弄到正确的二进制指令的,因为一些指令的操作对象就可能是错误的。

接口和针脚本质是一些数字表示的,需要通过这些数字来标识,所以我们还需要标识对应接口和针脚的文件。

安装和配置需要的工具

前提

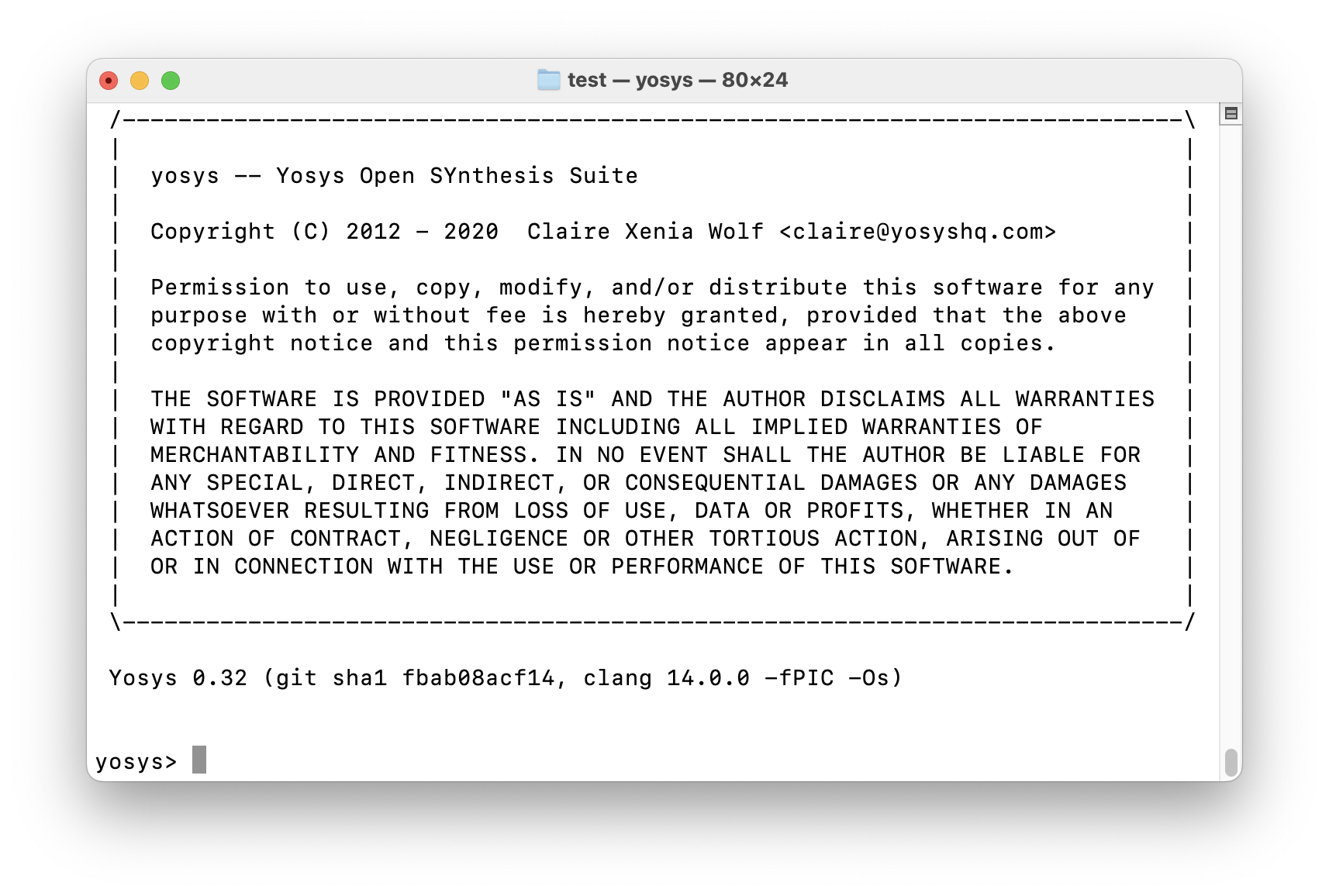

工具链 OSS CAD Suite

只安装 Gowin FPGA 需要的工具链

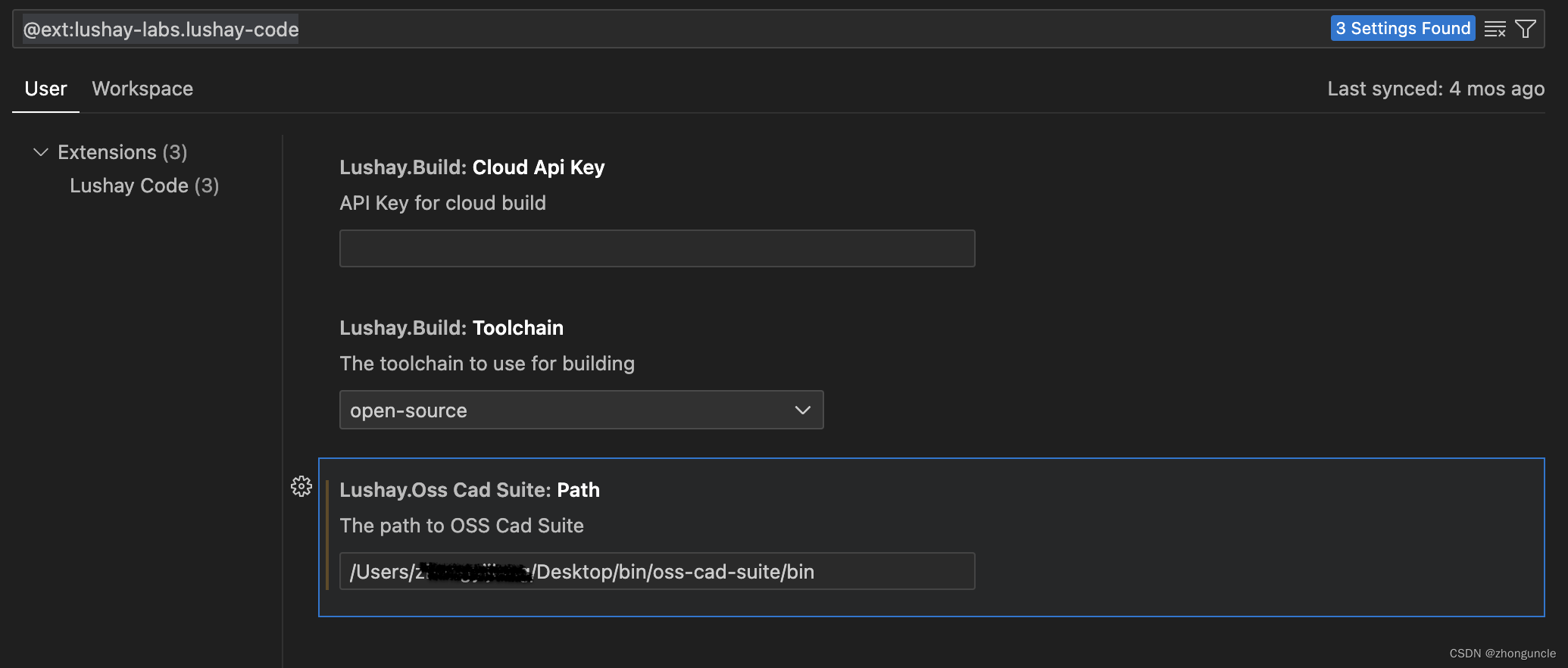

文本编辑器 VS Code

示例代码:让板载 LED 逐个亮起

构建项目

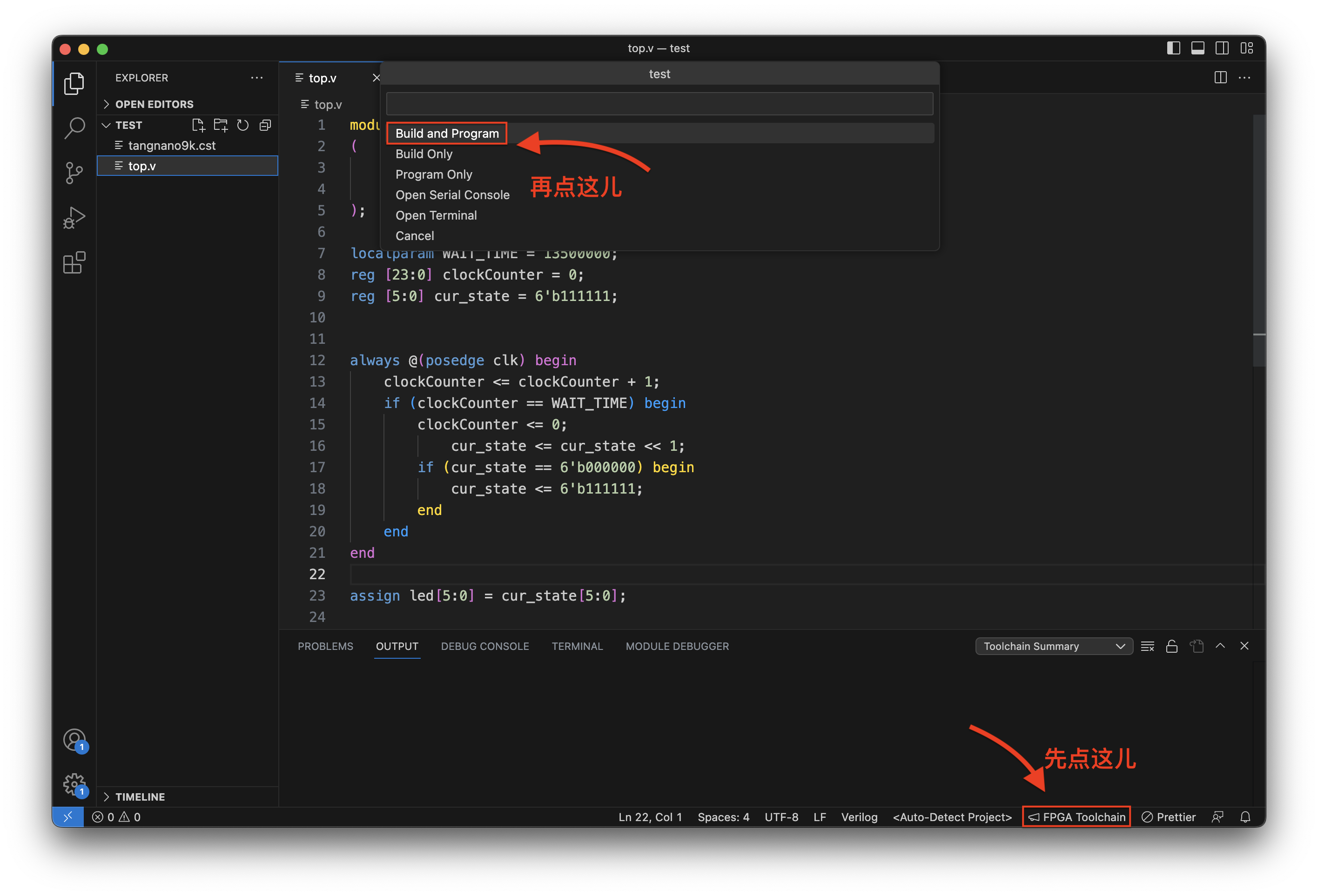

使用 VS Code 构建

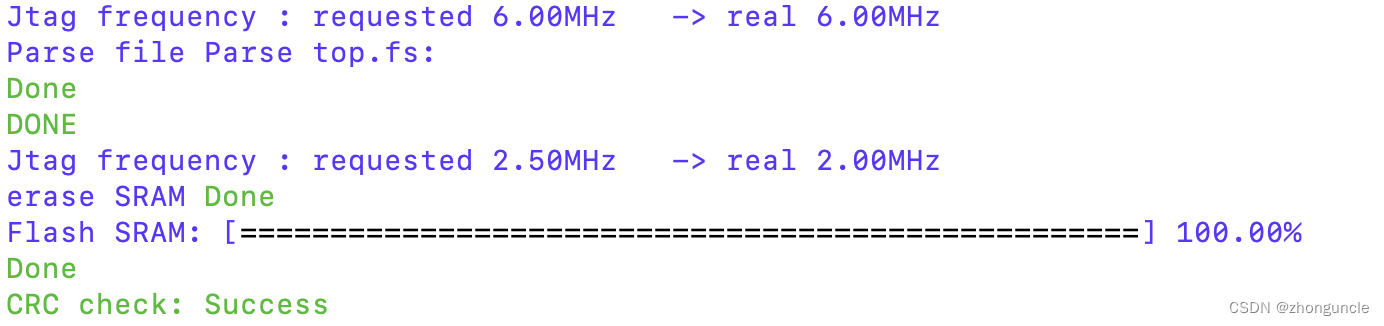

使用终端构建

逐步来说

写个脚本

扩展阅读

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。

![[嵌入式系统-6]:龙芯1B 开发学习套件 -3-软件层次架构](https://img-blog.csdnimg.cn/direct/df4bbd8d89544bc3a79ca254f68f58a1.png)