系列文章目录

分享一些fpga内使用riscv软核的经验,共大家参考。后续内容比较多,会做成一个系列。

前言

在efinix fpga中使用riscv是一件相对容易的事,efinix官方提供了一套集成riscv核心的应用IP,在IP catalog中可以很方便的生成、修改。裁剪IP的功能。

本文分享一套配置参数,包含时钟,memory,uart,spi,iic,gpio,axi,interrupt,usertimer等全部内容。

配置

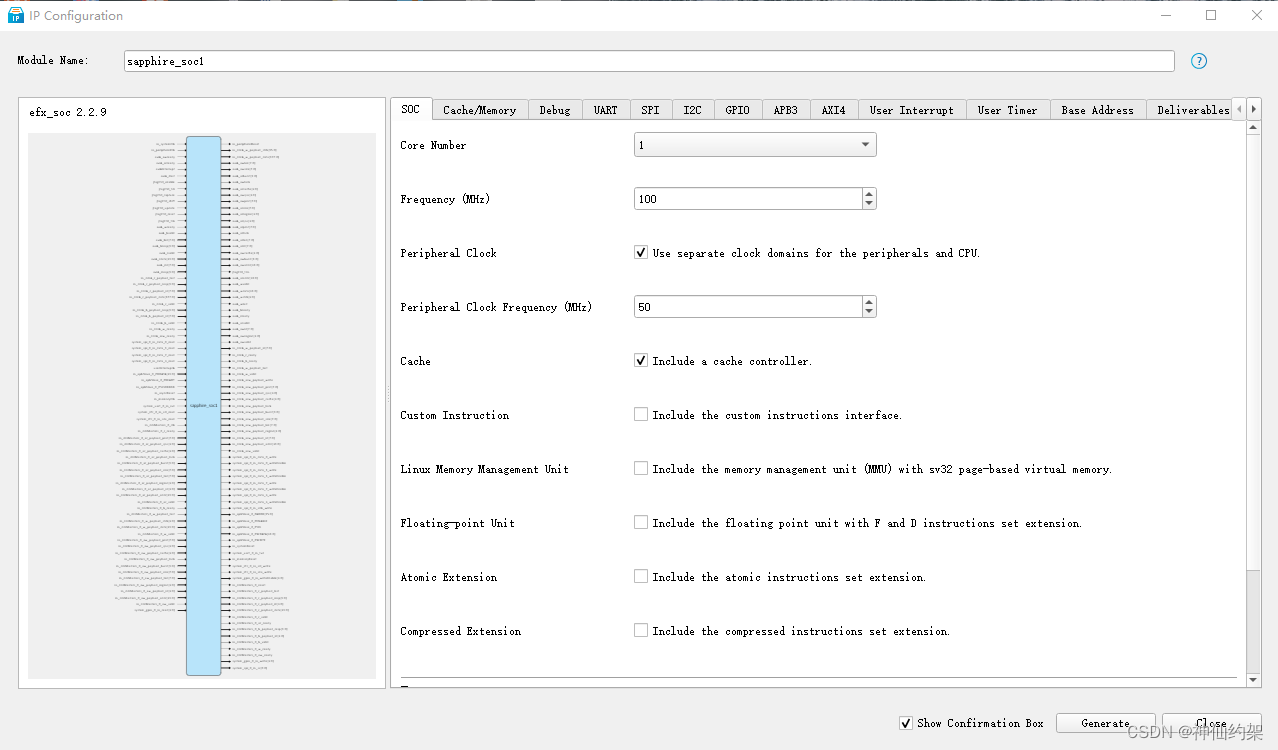

一、SOC

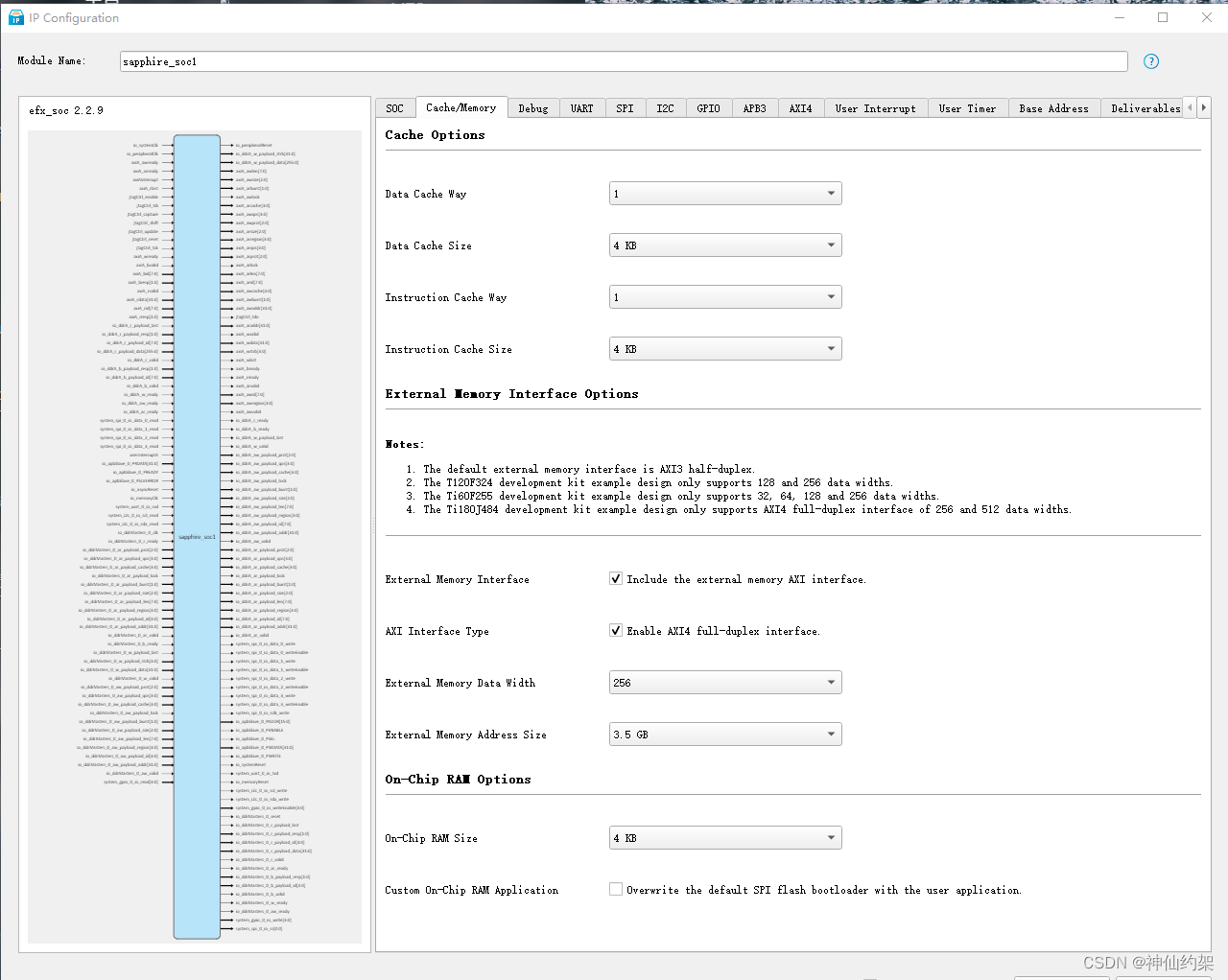

二、Cache/Memory

本设置使用axi4-full总线,位宽256bit,寻址3.5GB

On-chip RAM Size,bootloader的空间4kB,如果想在bootloader中多加一些功能,可以扩大这个空间到8KB

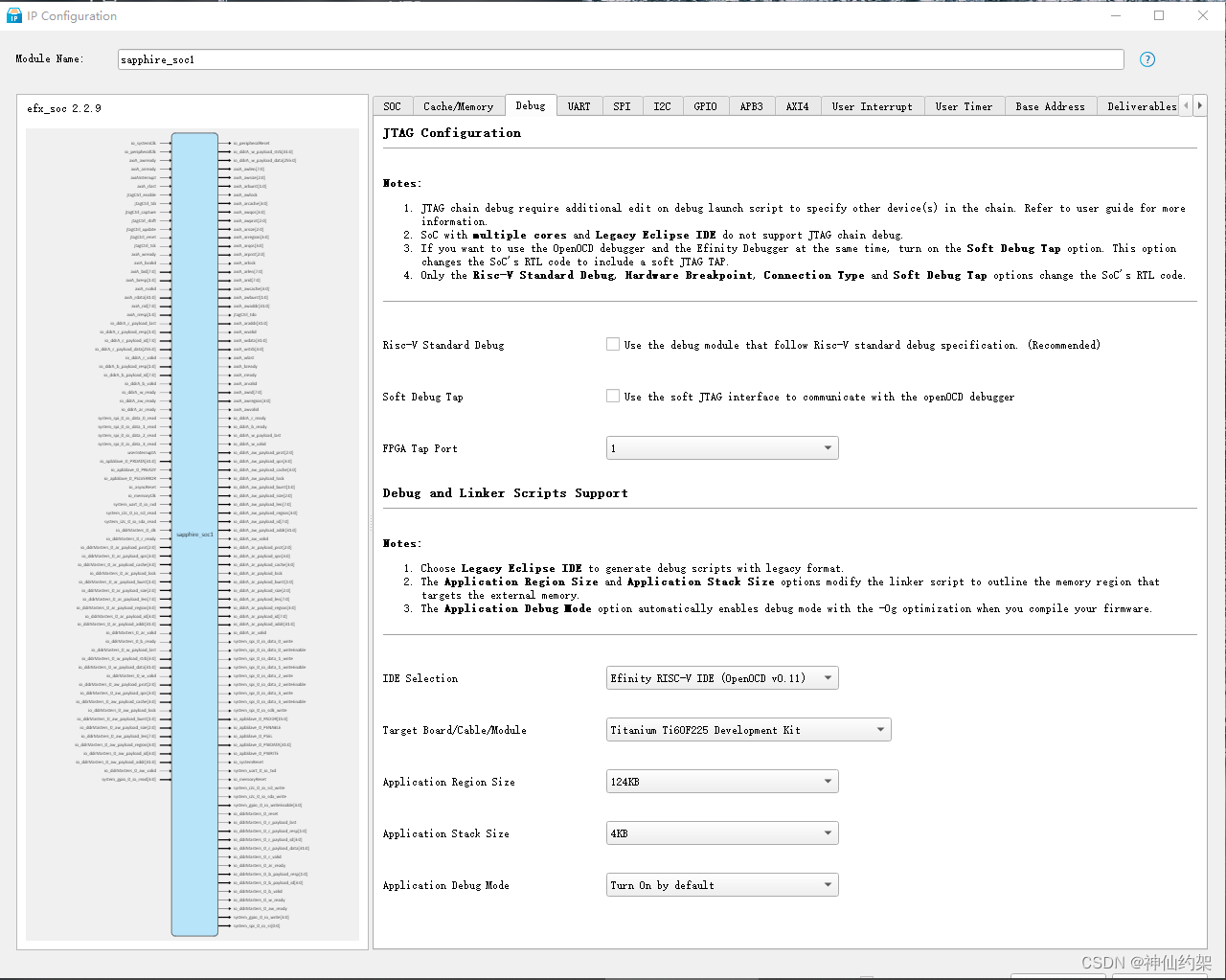

三、Debug

不使用。

四、UART

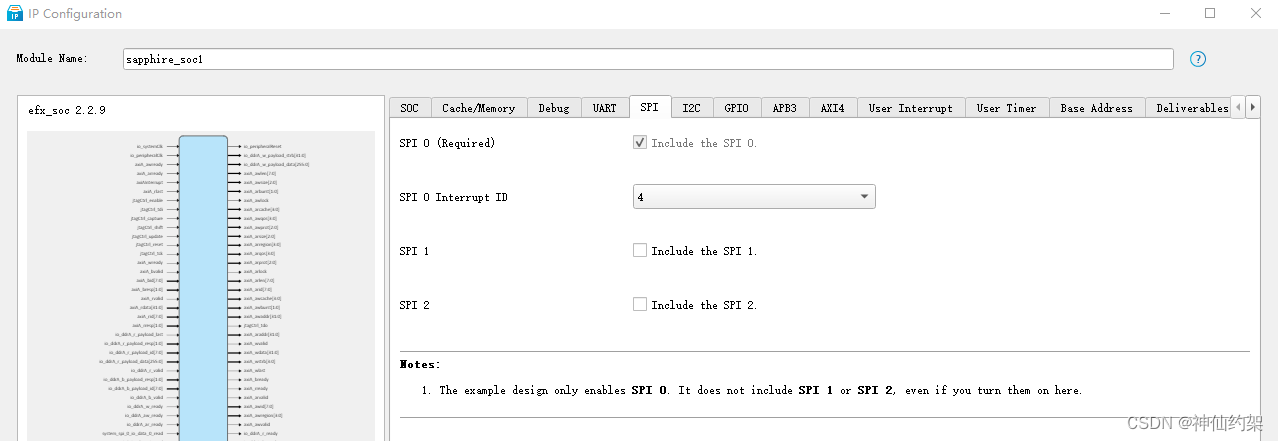

五、SPI

开通1个SPI

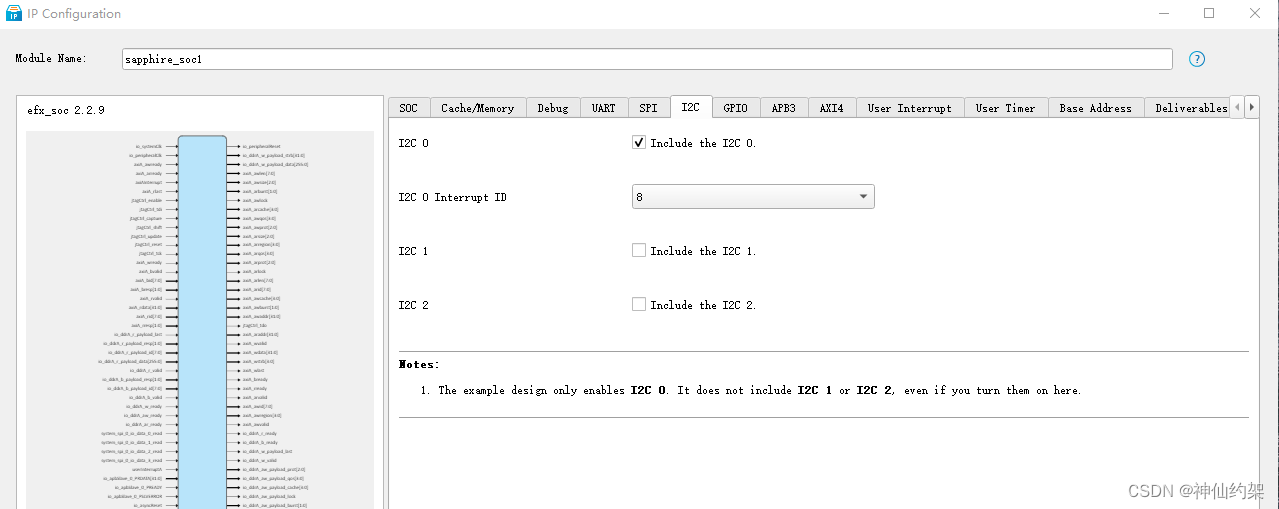

六、IIC

开通一个IIC

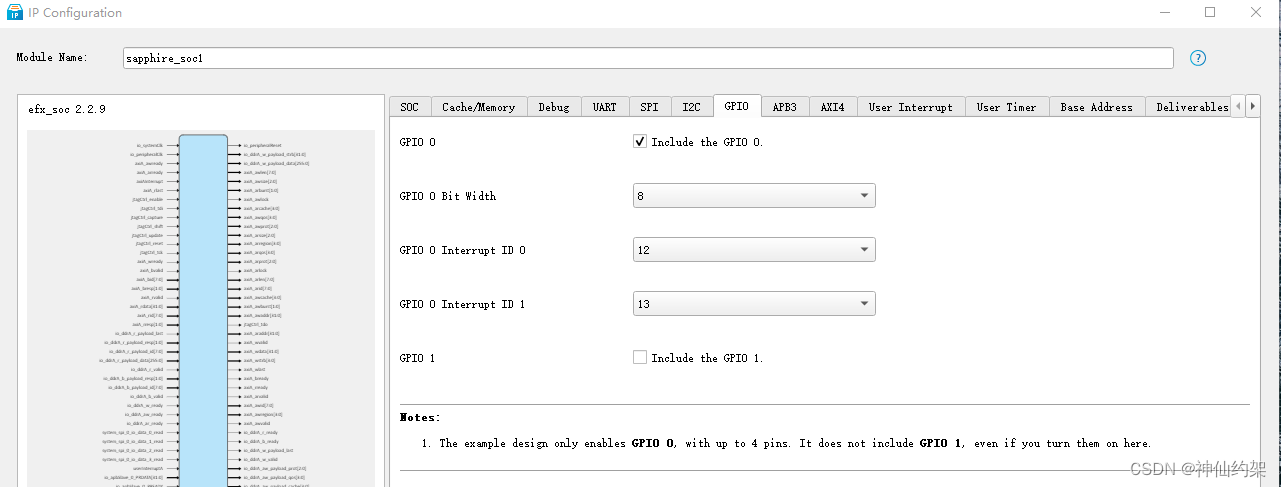

七、GPIO

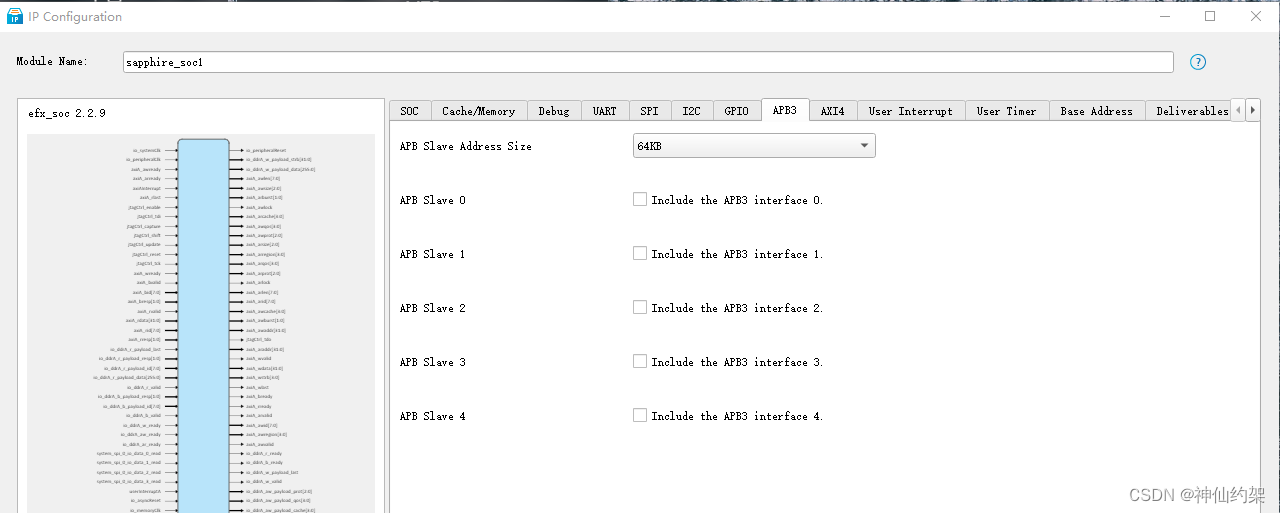

八、APB3

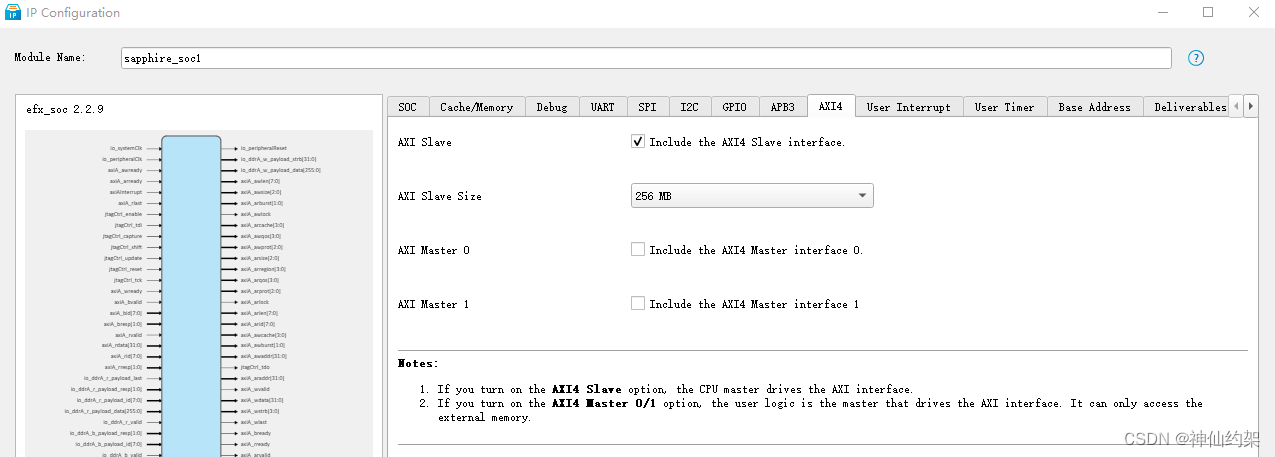

九、AXI4

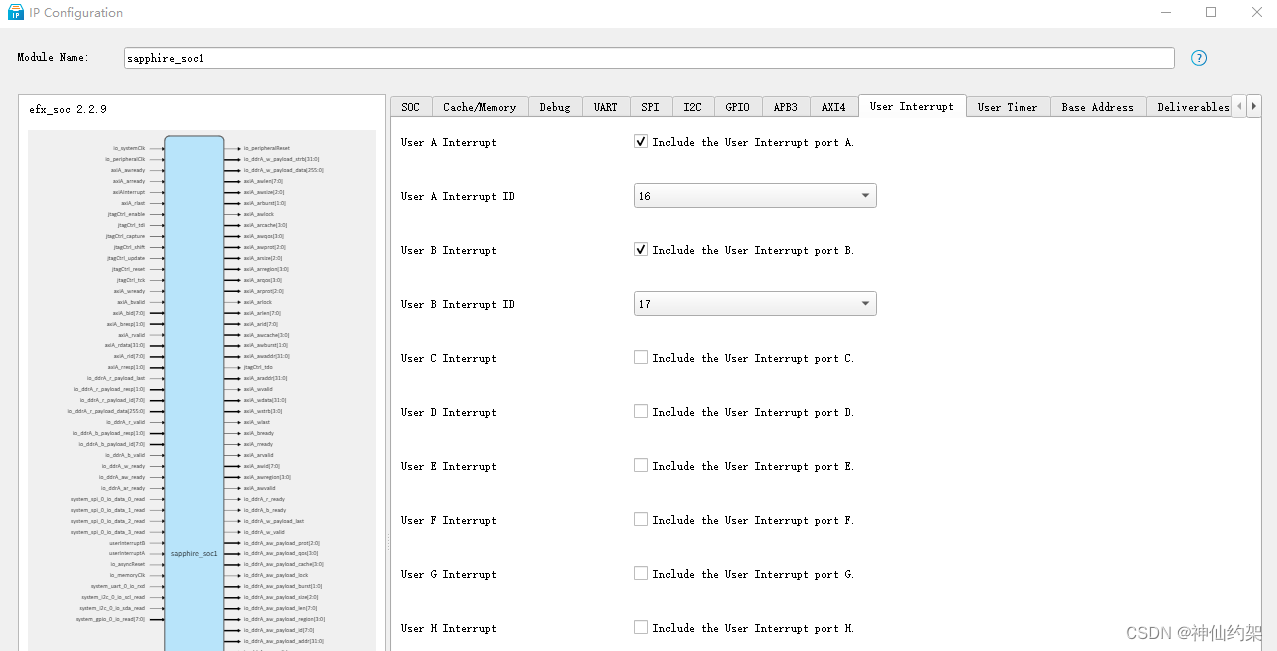

十、Interrupt

中断A、B

十一、User Timer

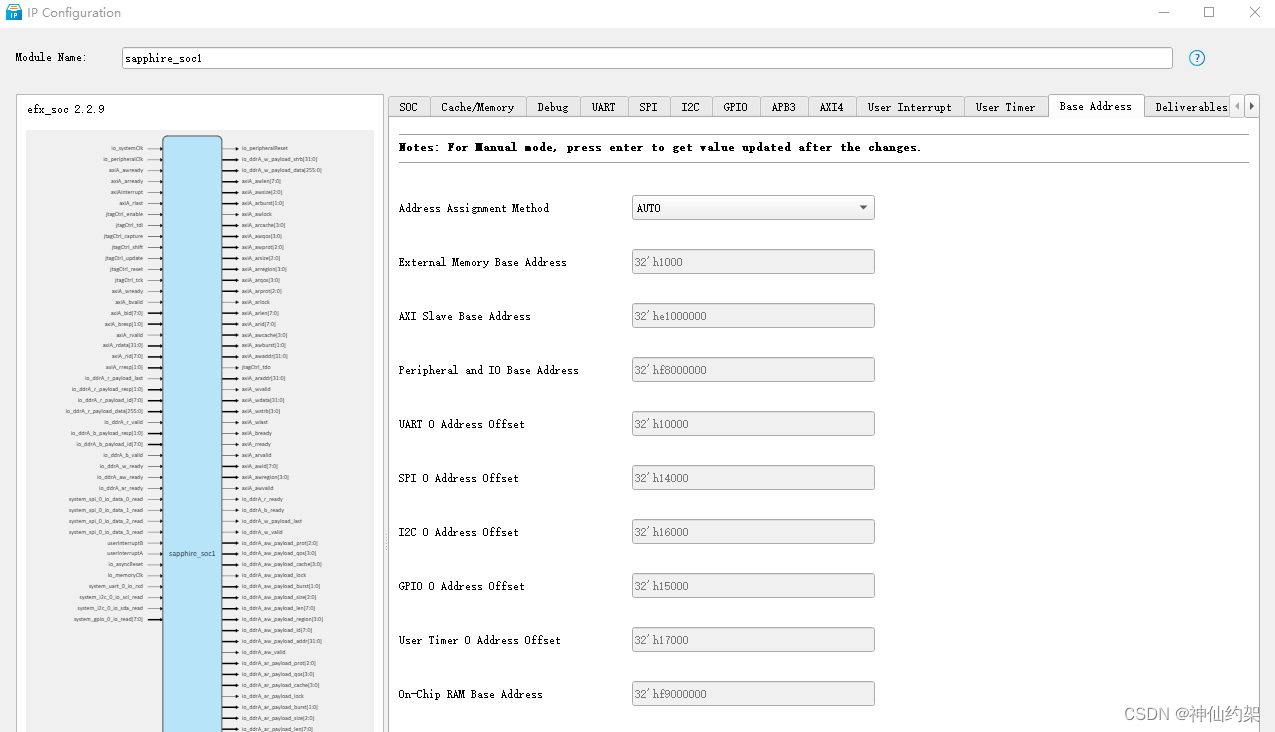

十二、Base address

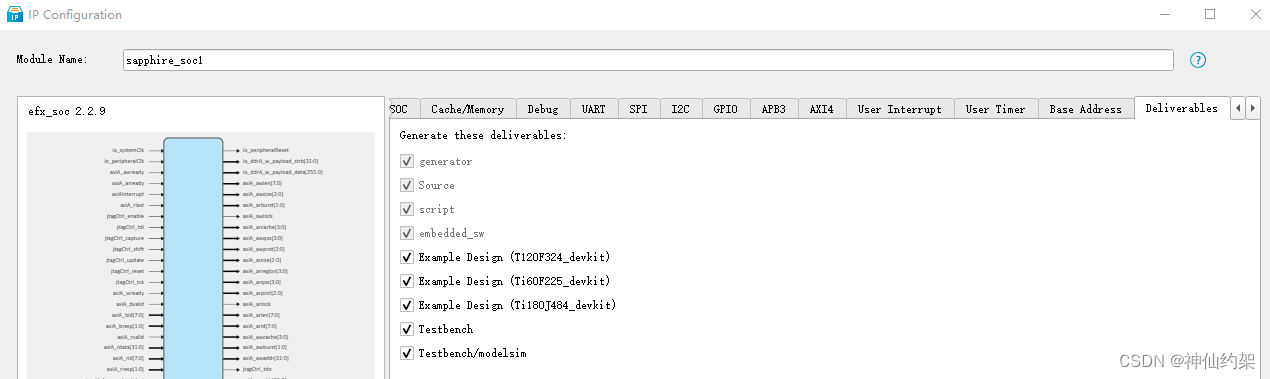

十三、Deliverables

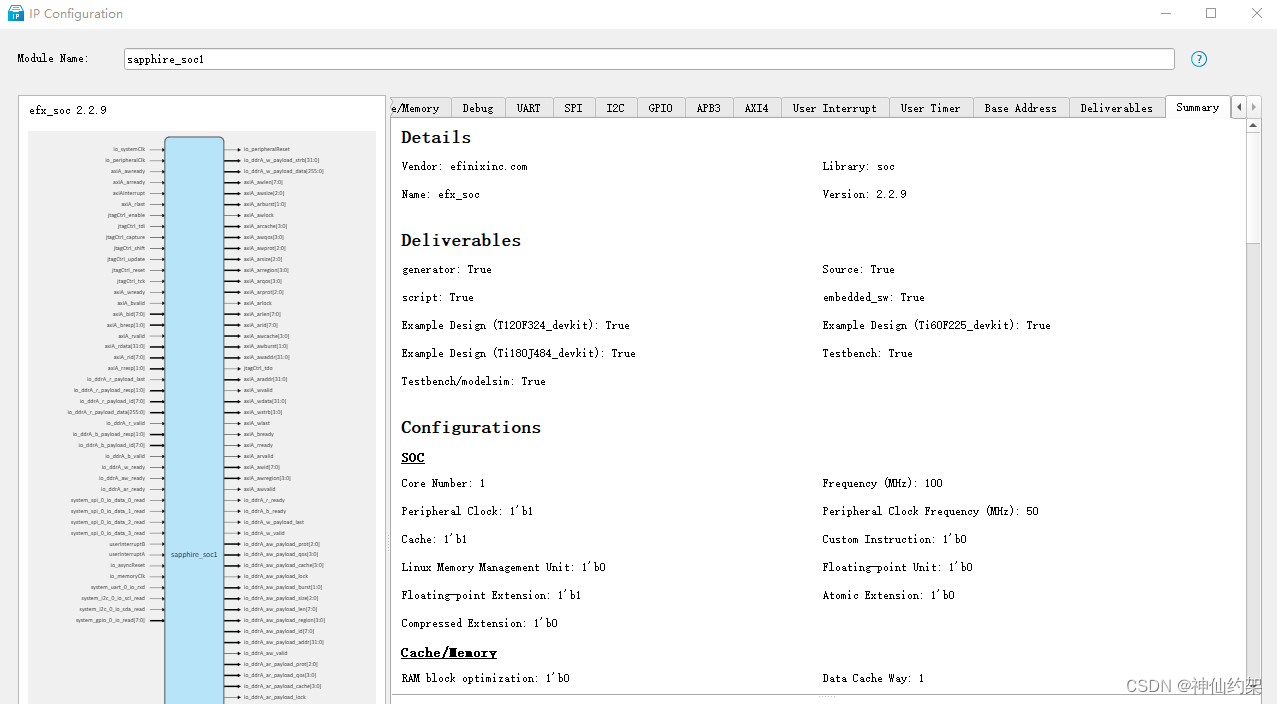

十四、SUmmary

原文地址:https://blog.csdn.net/sqqwm/article/details/134768099

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:http://www.7code.cn/show_38092.html

如若内容造成侵权/违法违规/事实不符,请联系代码007邮箱:suwngjj01@126.com进行投诉反馈,一经查实,立即删除!

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。