本文介绍: 在efinix fpga中使用riscv是一件相对容易的事,efinix官方提供了一套集成riscv核心的应用IP,在IP catalog中可以很方便的生成、修改。裁剪IP的功能。上一节我们在efinity IP catalog中选择生成了 riscv IP,在【Deliverables】页可见默认勾选了【embedded_sw】。本章节就产生的【embedded_sw】进行文件说明。

系列文章目录

分享一些fpga内使用riscv软核的经验,共大家参考。后续内容比较多,会做成一个系列。

【risc-v】易灵思efinix FPGA sapphire_soc IP配置参数分享-CSDN博客

【risc-v】易灵思efinix FPGA riscv 时钟配置的一些总结-CSDN博客

前言

源码文件夹的生成

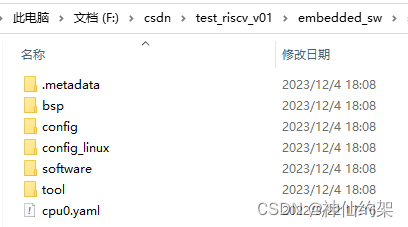

文件说明

【BSP】

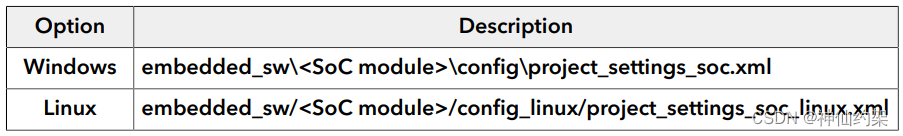

【config】和【config_linux】

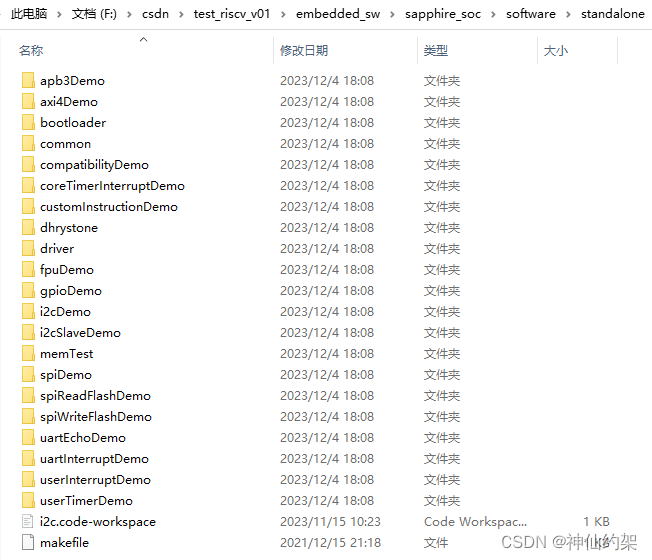

【software】

延伸

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。