lscpu命令的使用

在Linux系统上使用lscpu命令,会显示当前系统中处理器的相关信息,包括处理器架构、CPU频率、CPU核心数、线程数、缓存大小、字节序等等,可以很好的了解系统的处理能力和硬件配置情况,下面是一些常见的输出解释:

Architecture: 显示系统处理器的架构,比如x86_64或ARM64等等。

CPU(s): 显示系统中的CPU个数。

Thread(s) per core: 显示每个CPU核心的线程数,即超线程技术的线程数。

Core(s) per socket: 显示每个CPU插槽中的CPU核心数。

Socket(s): 显示系统中的CPU插槽数量。

L1d cache, L1i cache, L2 cache, L3 cache: 显示各级CPU缓存的大小。

Byte Order: 显示系统使用的字节序(大端序或小端序)。

# lscpu

Architecture: x86_64,表示系统的处理器架构为x86-64。

CPU op-mode(s): 32-bit, 64-bit,表示处理器支持32位和64位操作系统。

Byte Order: Little Endian,表示系统使用的字节序为小端序。

CPU(s): 96,表示系统中有96个CPU核心。

On-line CPU(s) list: 0-95,表示所有CPU核心都处于在线状态。

Thread(s) per core: 2,表示每个CPU核心都支持2个线程,即超线程技术。

Core(s) per socket: 24,表示每个CPU插槽中有24个CPU核心。

Socket(s): 2,表示系统中有2个CPU插槽。

NUMA node(s): 2,表示系统中有2个NUMA节点。

Vendor ID: GenuineIntel,表示CPU供应商为英特尔公司。

CPU family: 6,表示CPU家族为英特尔的第六代家族。

Model: 85,表示CPU型号为85。

Model name: Intel(R) Xeon(R) Platinum 8255C CPU @ 2.50GHz,表示CPU型号为Intel Xeon Platinum 8255C,主频为2.5 GHz。

Stepping: 7,表示CPU的步进。

CPU MHz: 2501.000,表示CPU当前主频为2501 MHz。

CPU max MHz: 2501.0000,表示CPU最大主频为2501 MHz。

CPU min MHz: 1000.0000,表示CPU最小主频为1000 MHz。

BogoMIPS: 5000.00,表示系统的BogoMIPS指标。

Virtualization: VT-x,表示CPU支持虚拟化技术VT-x。

L1d cache: 32K,表示CPU的一级数据缓存大小为32KB。

L1i cache: 32K,表示CPU的一级指令缓存大小为32KB。

L2 cache: 1024K,表示CPU的二级缓存大小为1MB。

L3 cache: 36608K,表示CPU的三级缓存大小为36MB。

NUMA node0 CPU(s): 0-23,48-71,表示NUMA节点0中CPU核心的ID号为0-23和48-71。

NUMA node1 CPU(s): 24-47,72-95,表示NUMA节点1中CPU核心的ID号为24-47和72-95。

# 表示CPU的功能特性,包括fpu、vme、de、pse、tsc、msr、pae等等。

Flags: fpu vme de pse tsc msr pae mce cx8 apic sep mtrr pge mca cmov pat pse36 clflush dts acpi mmx fxsr sse sse2 ss ht tm pbe syscall nx pdpe1gb rdtscp lm constant_tsc art arch_perfmon pebs bts rep_good nopl xtopology nonstop_tsc aperfmperf eagerfpu pni pclmulqdq dtes64 monitor ds_cpl vmx smx est tm2 ssse3 sdbg fma cx16 xtpr pdcm pcid dca sse4_1 sse4_2 x2apic movbe popcnt tsc_deadline_timer aes xsave avx f16c rdrand lahf_lm abm 3dnowprefetch epb cat_l3 cdp_l3 invpcid_single intel_ppin intel_pt ssbd mba ibrs ibpb stibp ibrs_enhanced tpr_shadow vnmi flexpriority ept vpid fsgsbase tsc_adjust bmi1 hle avx2 smep bmi2 erms invpcid rtm cqm mpx rdt_a avx512f avx512dq rdseed adx smap clflushopt clwb avx512cd avx512bw avx512vl xsaveopt xsavec xgetbv1 cqm_llc cqm_occup_llc cqm_mbm_total cqm_mbm_local dtherm ida arat pln pts pku ospke avx512_vnni md_clear spec_ctrl intel_stibp flush_l1d arch_capabilities,

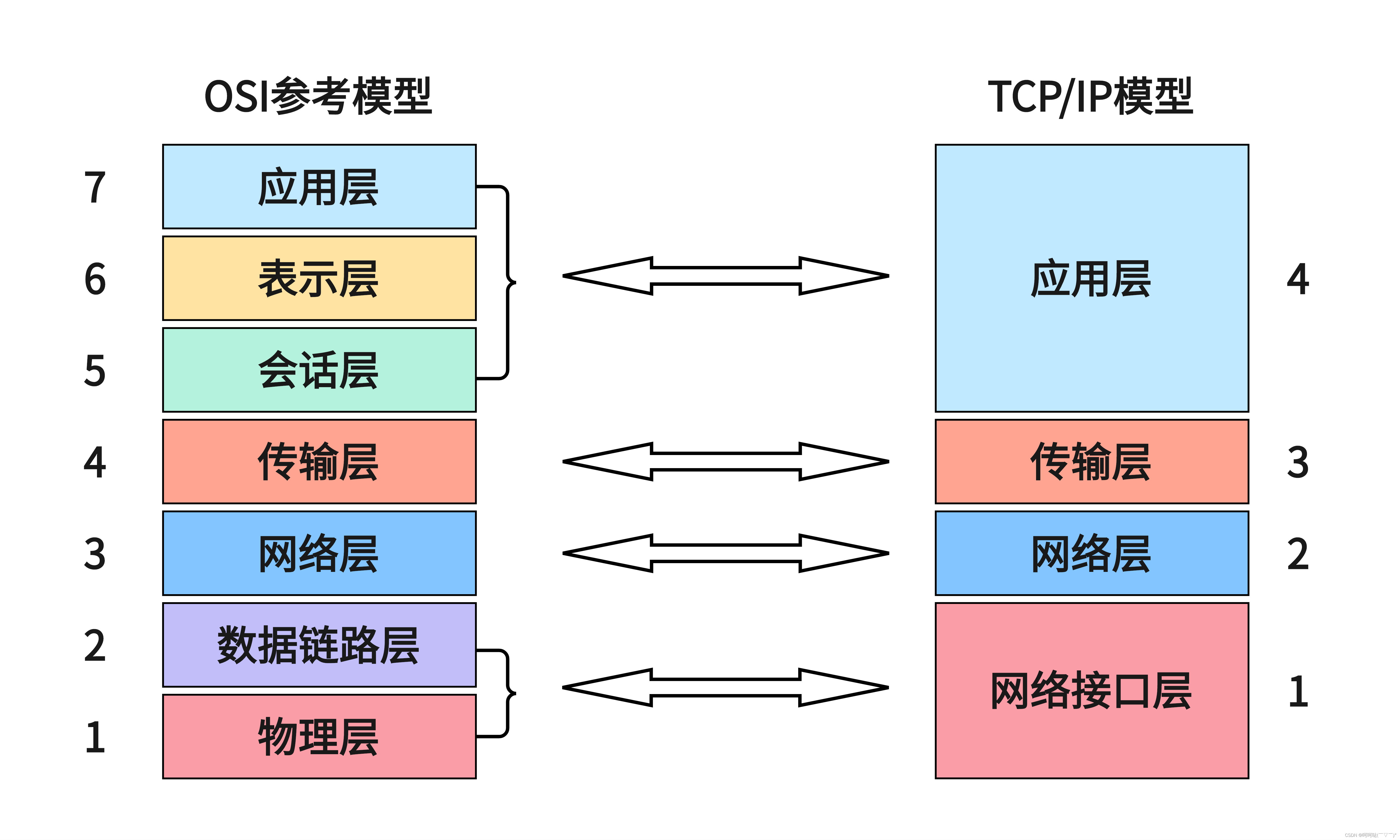

什么是NUMA

NUMA (Non-Uniform Memory Access) 是一种计算机系统架构,其目的是优化多处理器系统中内存访问的效率。在 NUMA 架构中,系统中的物理内存被分割成多个区域,每个区域被称为一个 NUMA 节点。每个 NUMA 节点都与一组 CPU 和一些 I/O 设备关联。

在 NUMA 架构中,每个 CPU 有自己的本地内存,同时也可以访问其他 CPU 的内存。但是,由于距离不同 NUMA 节点的内存的距离不同,因此访问不同 NUMA 节点的内存所需的时间和带宽也会有所不同。因此,对于访问本地 NUMA 节点的内存,访问速度更快,而对于访问远程 NUMA 节点的内存,则访问速度更慢。

为了最大化系统的性能,NUMA 架构中的软件和操作系统需要将内存访问负载分配给本地 NUMA 节点中的 CPU,以尽量减少访问远程 NUMA 节点的内存的需求。此外,一些应用程序也可以通过 NUMA 感知编程来充分利用 NUMA 架构,从而提高性能。

NUMA节点与cpu插槽的关系

在 NUMA 架构中,每个 NUMA 节点都与一组 CPU 关联。每个 CPU 插槽可以安装一个或多个 CPU 芯片,每个 CPU 芯片可以包含一个或多个 CPU 核心。

在一些 NUMA 系统中,每个 CPU 插槽可能只与一个 NUMA 节点关联,因此一个 NUMA 节点只能包含一个 CPU 插槽中的 CPU 芯片。在其他系统中,一个 NUMA 节点可能会与多个 CPU 插槽关联,每个 CPU 插槽中的 CPU 芯片可能会共享该 NUMA 节点中的内存。

总之,CPU 插槽和 NUMA 节点之间的关系取决于系统的具体架构和设计。在一些系统中,CPU 插槽和 NUMA 节点可能是一一对应的,而在其他系统中,则可能存在多个 CPU 插槽共享一个 NUMA 节点的情况。

原文地址:https://blog.csdn.net/weixin_43702146/article/details/130618465

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:http://www.7code.cn/show_41422.html

如若内容造成侵权/违法违规/事实不符,请联系代码007邮箱:suwngjj01@126.com进行投诉反馈,一经查实,立即删除!