本文介绍: 欢迎来到Cache(缓存)的世界!自从世界第一台计算机诞生之日起,人们对效率的渴望逐步增强。从CPU到存储,从芯片到内存,一批又一批的先驱以一种孜孜不倦的“工匠”精神,为计算机运行效率的提升做出了不可磨灭的贡献。从而也为世界各国计算机的快速发展和普及铺平了道路,迎来了发展的春天!本期主题,博主带着大家了解Cache,进而掌握如何使用Cache。首先,按惯例,请允许微服务大家族成员前来报到。微服务实战系列之Nginx(技巧篇)微服务实战系列之Nginx微服务实战系列之Feign。

前言

本期主题,博主带着大家了解Cache,进而掌握如何使用Cache。

首先,按惯例,请允许微服务大家族成员前来报到。如有需要请回看,欢迎三连:

提到Cache,各位盆友,可联想到什么?

欢迎开始今天的旅程,允许博主带着各位盆友“逛一逛”,探一下Cache的内幕。

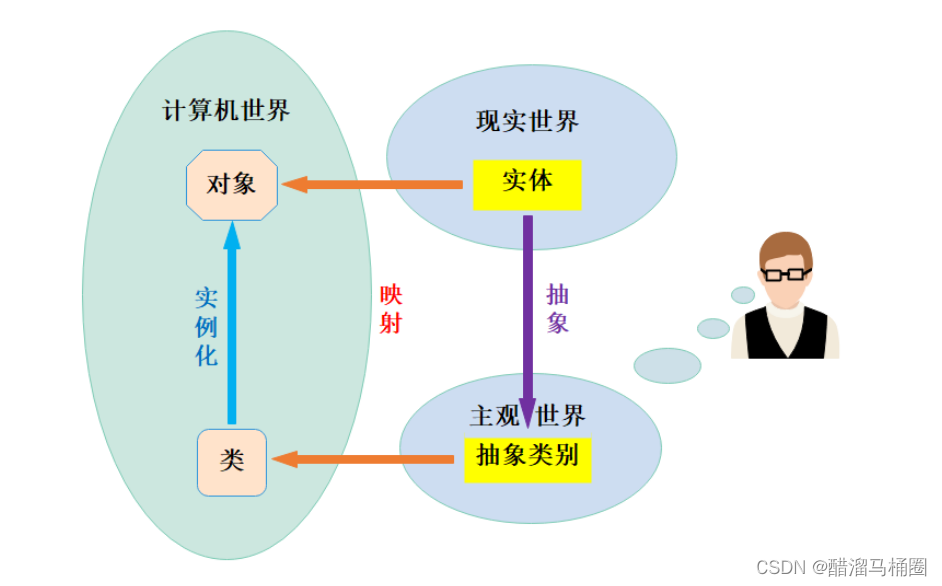

一、Cache简介

因此它具备几个特征:

二、Cache核心

1. 数据共享

2. 多层级

3. 一致性

4. 时效性

结语

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。