本文介绍: 方法:FIFO_TX无数据,输出默认未知值,那么在程序启动时候先往FIFO_TX写入足够TTL_TX发送1~2ms的数据,STM32读写FPGA任务优先级调高,接收到FIFO_RX快满中断读写时间误差在1~2ms以内,那么TTL_TX发送的数据一定是TTL_RX接收的数据。原因:STM32读FPGA过程中,FIFO_RX中数据剩余1023个,快满标志清零了,但FIFO_RX刚好这时候又采集到TTL_RX数据,恢复到1024个,再次触发快满标志,造成STM32读2*1000数据。④FIFO_RX出现满标志。

1、实现功能:

FPGA芯片两个信号管脚分别是TTL_RX与TTL_TX,stm32读取FPGA采集信号TTL_RX的数据,再写到FPGA中通过TTL_TX发送出去,实现FPGA串口功能

2、大概方法:

①、FPGA中FIFO_RX和FIFO_TX,分别负责TTL_RX采集接收与TTL_TX发送功能

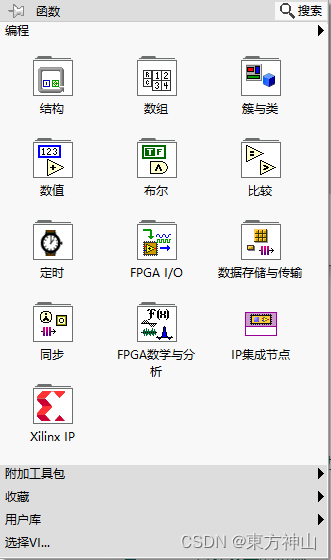

②、stm32通过FSMC nand flash 驱动与FPGA通讯,读取FIFO_RX接收到的数据,把想发送的数据写入FIFO_TX中

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。