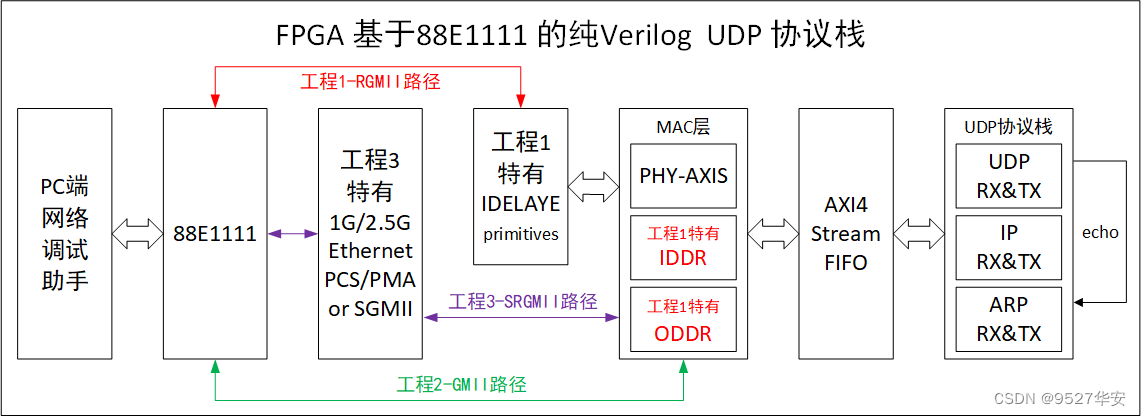

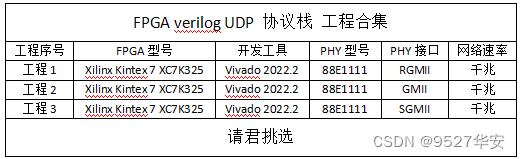

FPGA UDP协议栈:基于88E1111,支持RGMII、GMII、SGMII三种模式,提供3套工程源码和技术支持

1、前言

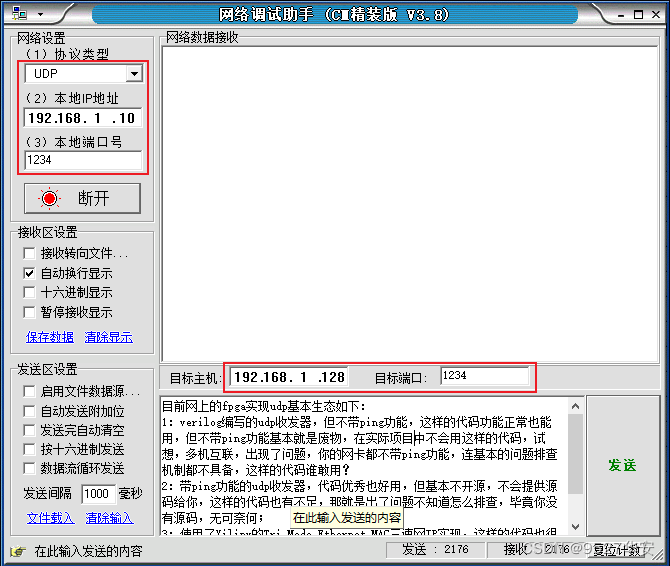

目前网上的fpga实现udp基本生态如下:

1:verilog编写的udp收发器,但中间的FIFO或者RAM等调用了IP,或者不带ping功能,这样的代码功能正常也能用,但不带ping功能基本就是废物,在实际项目中不会用这样的代码,试想,多机互联,出现了问题,你的网卡都不带ping功能,连基本的问题排查机制都不具备,这样的代码谁敢用?

2:带ping功能的udp收发器,代码优秀也好用,但基本不开源,不会提供源码给你,这样的代码也有不足,那就是出了问题不知道怎么排查,毕竟你没有源码,无可奈何;

3:使用了Xilinx的Tri Mode Ethernet MAC三速网IP实现,这样的代码也很优秀,但还是那个问题,没有源码,且三速网IP需要licence,三速网IP实现了rgmii到gmii再到axis的转换;

4:使用FPGA的GTX资源利用SFP光口实现UDP,通信,这种方案不需要外接网络变压器即可完成;

5:真正意义上的verilog实现的UDP协议栈,真正意义上的verilog实现意思是UDP协议栈全部代码均使用verilog代码,不适用任何IP核,包括FIFO、RAM等,这样的UDP协议栈移植性很强,这样的协议栈在市面上也很少,几乎很难得到,而很设计就是这样的协议栈,呵呵。。。

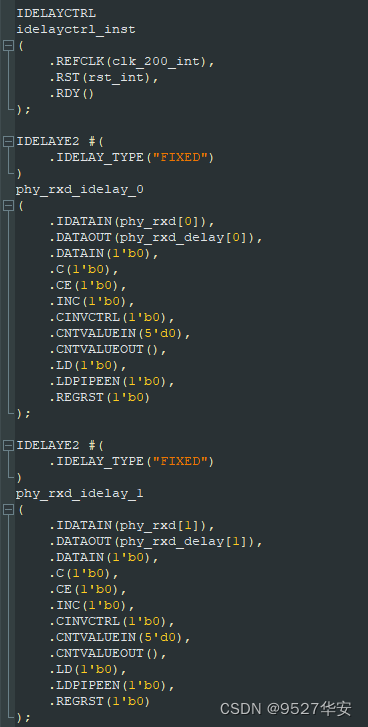

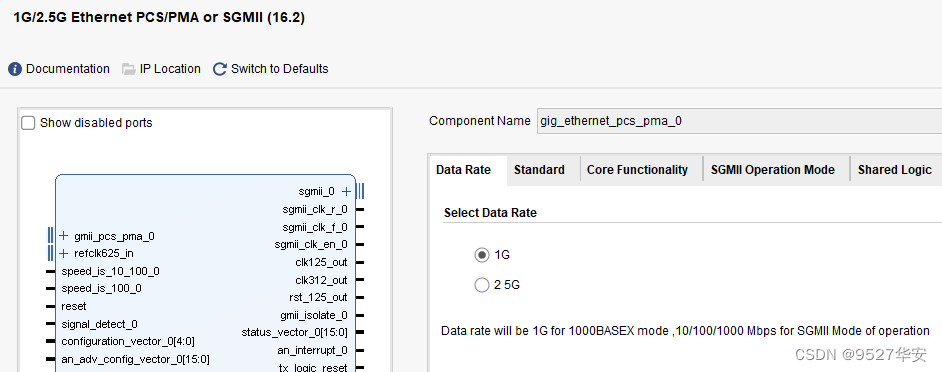

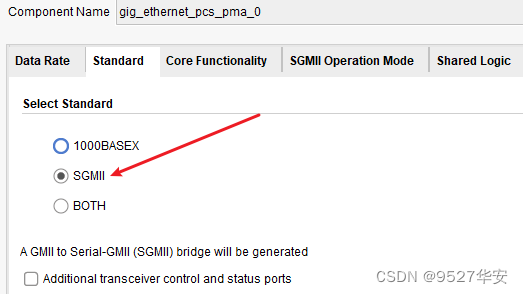

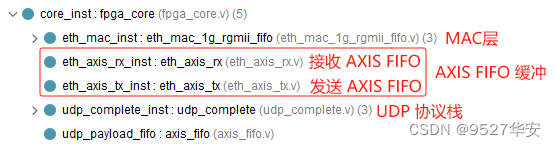

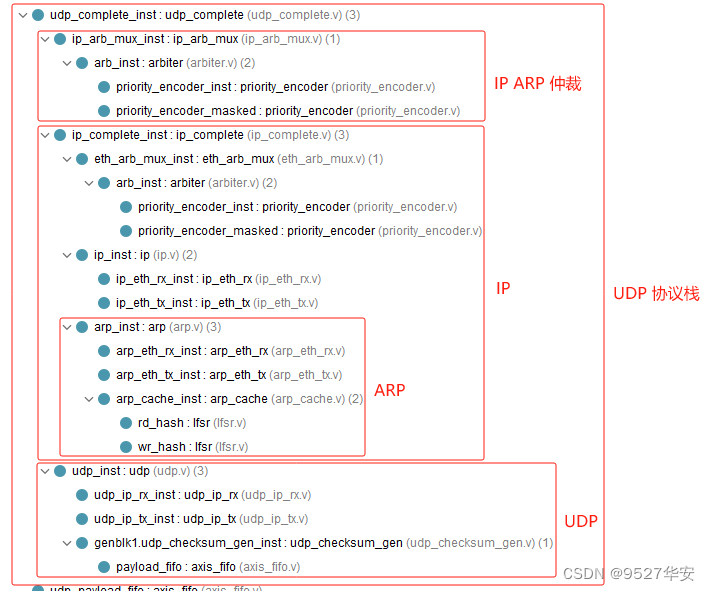

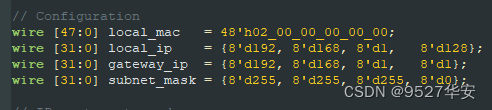

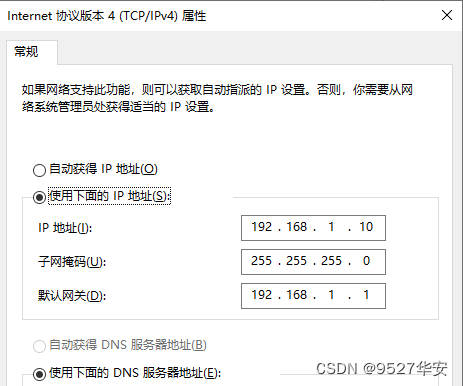

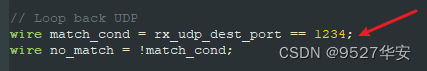

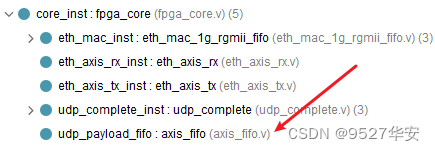

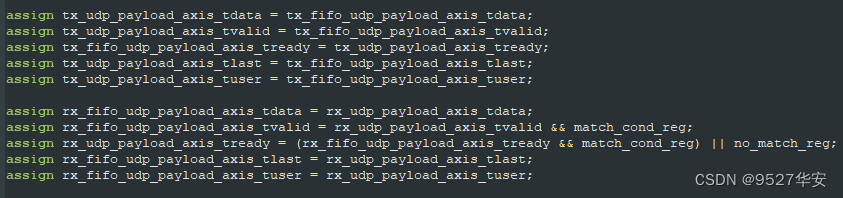

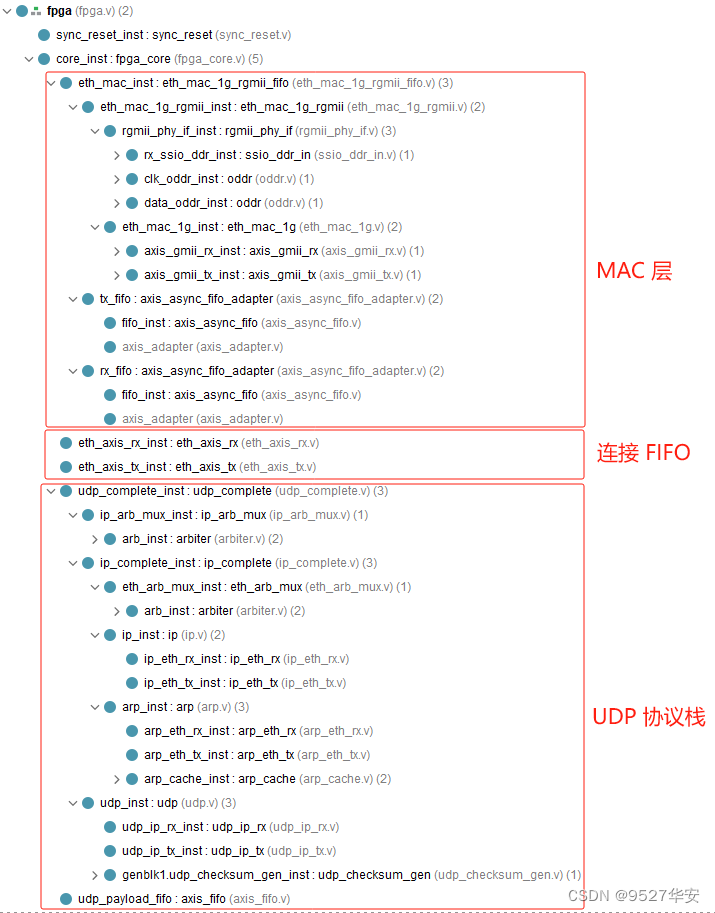

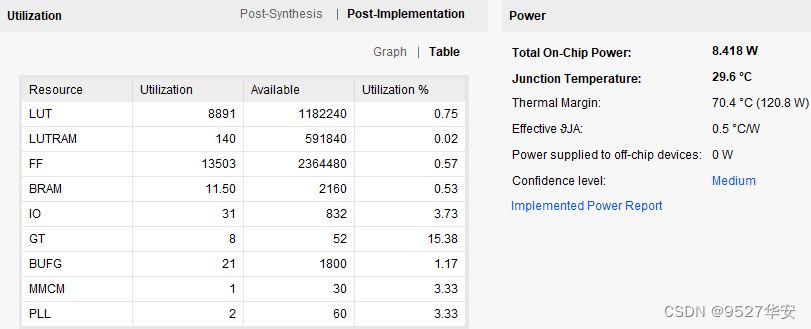

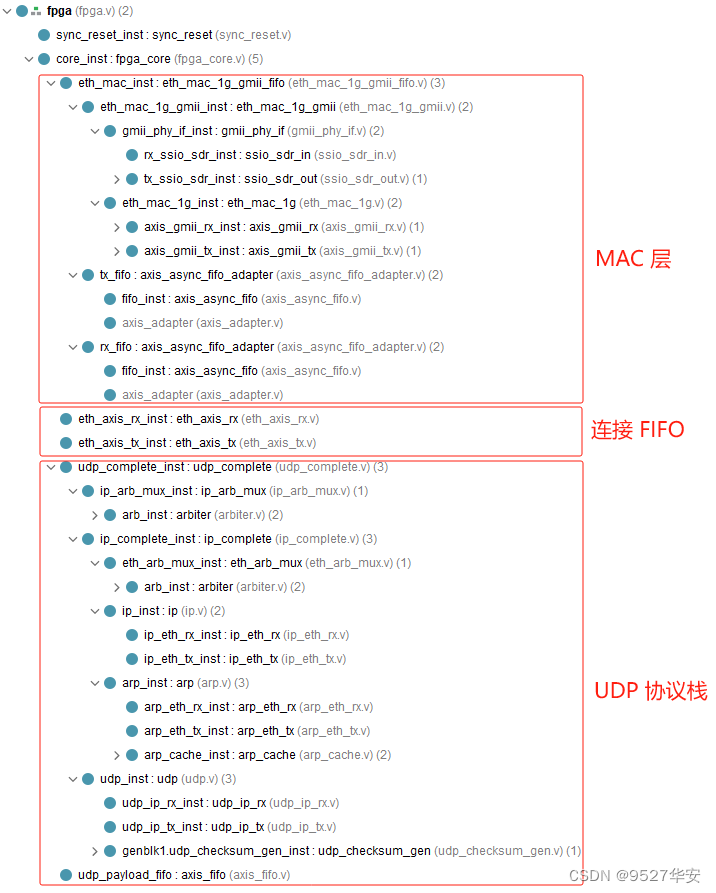

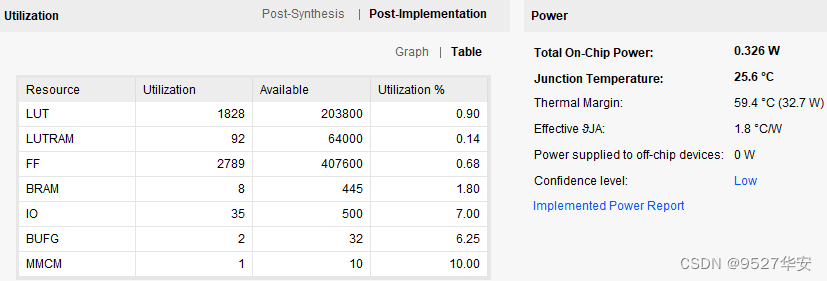

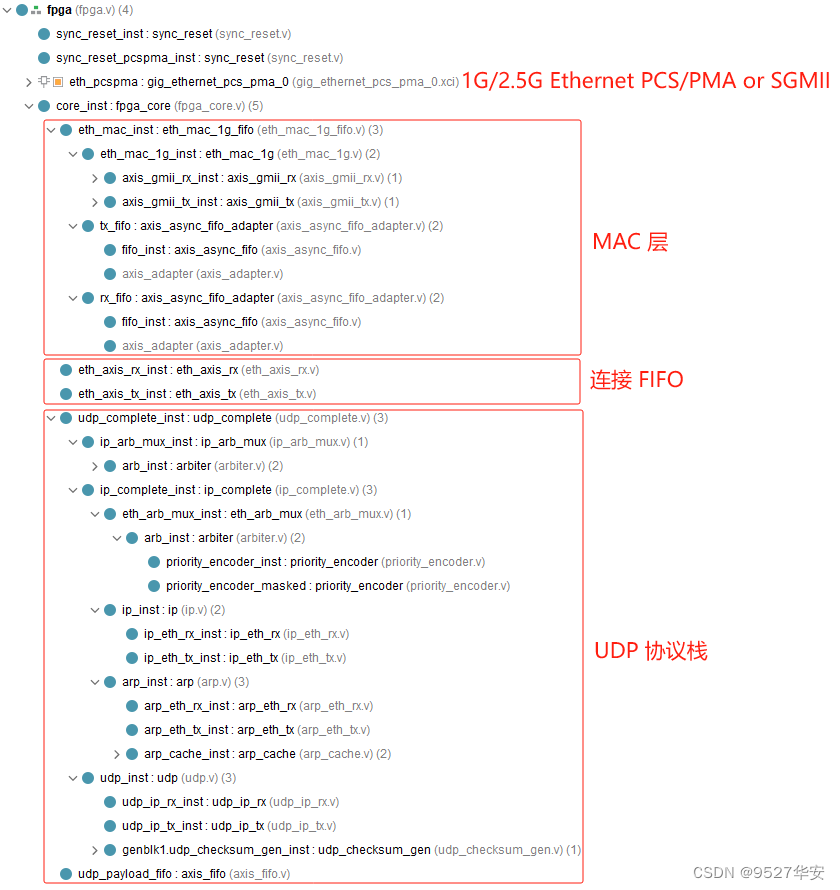

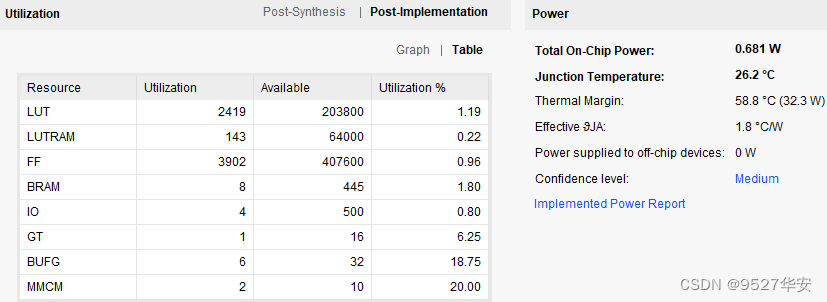

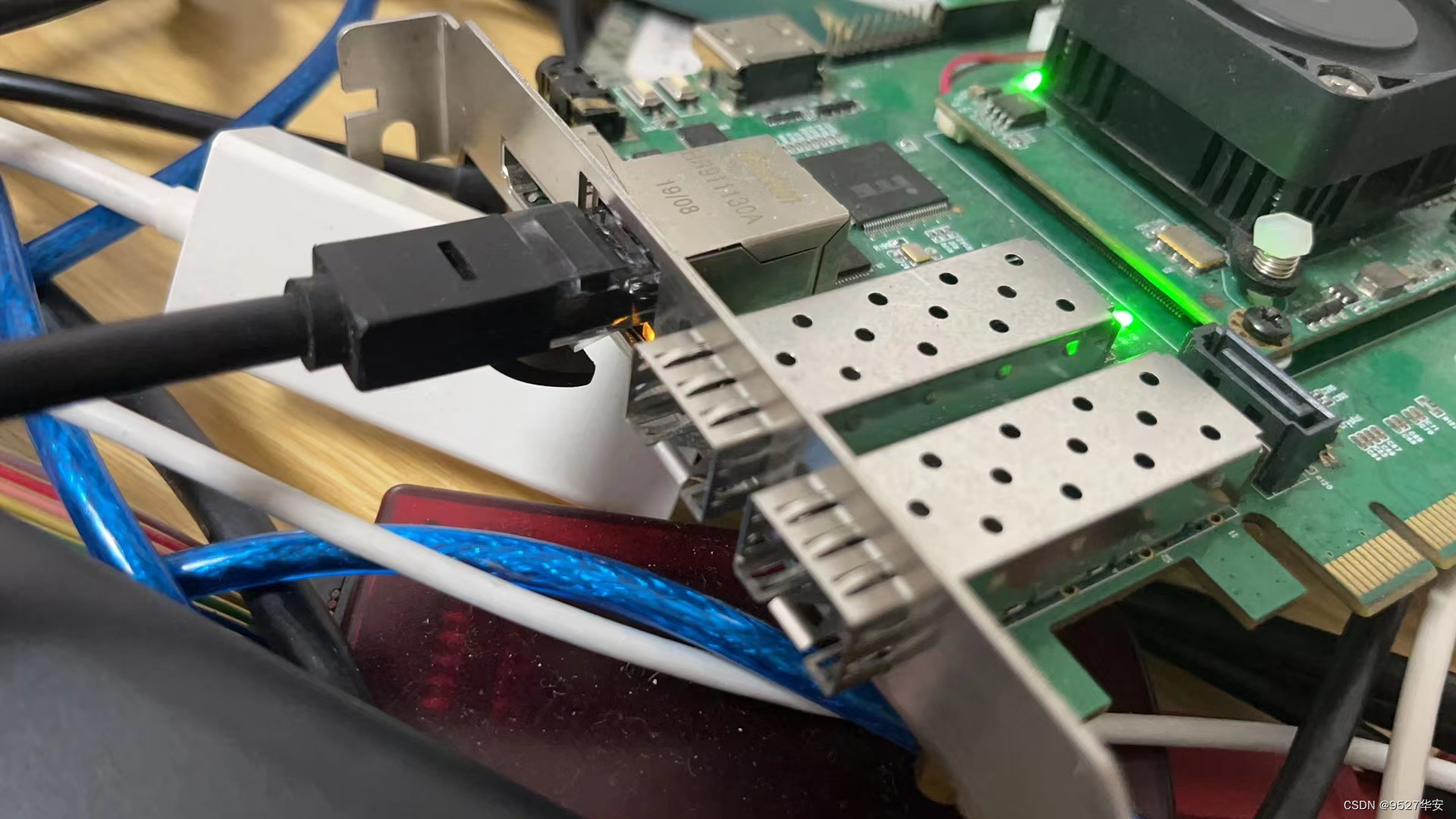

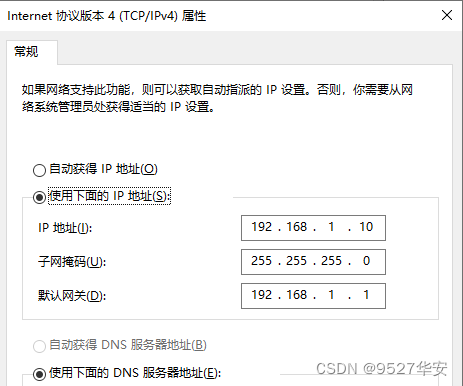

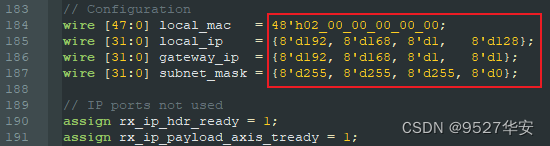

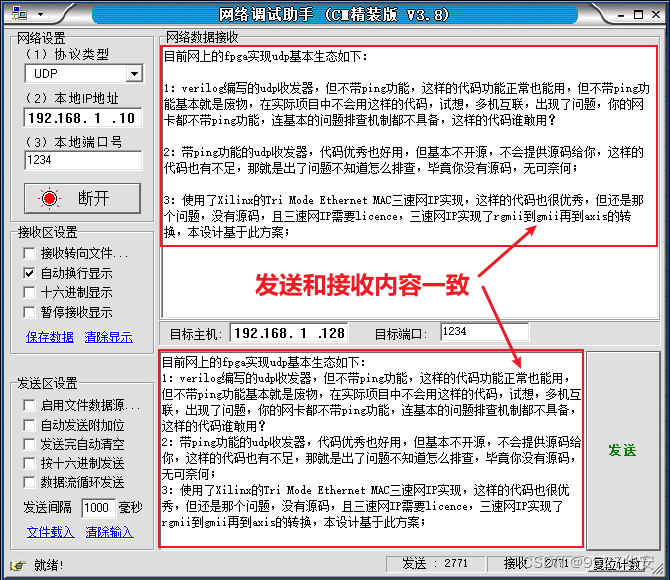

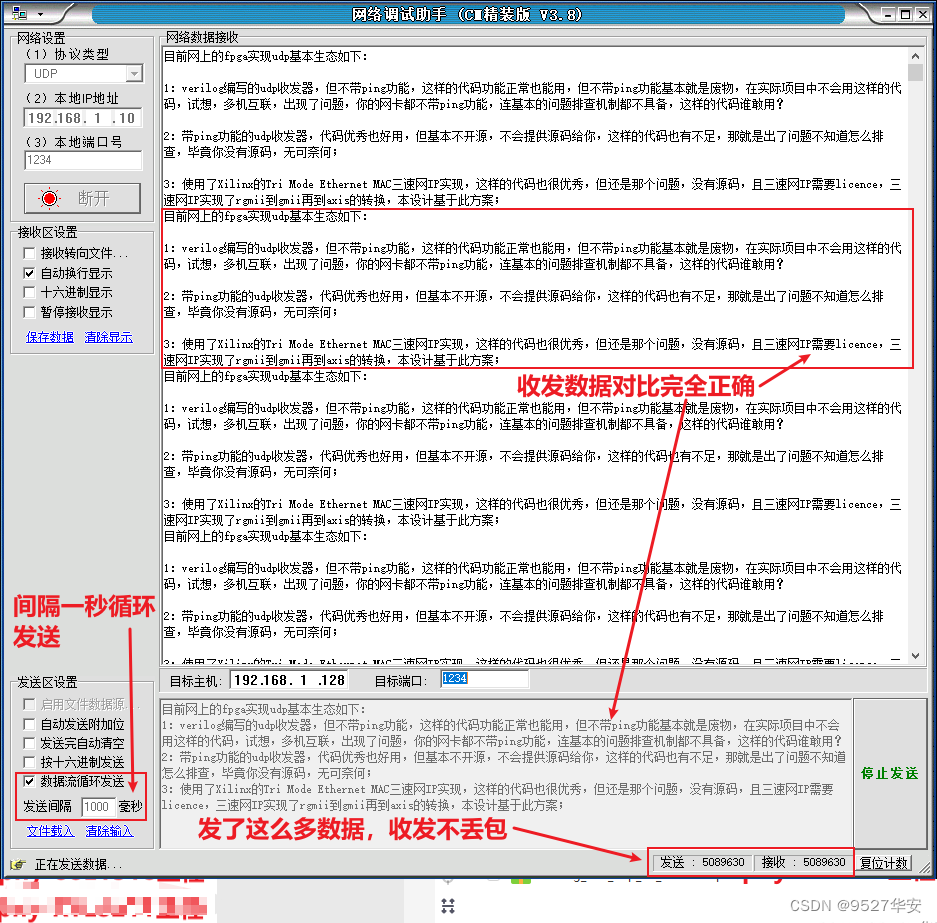

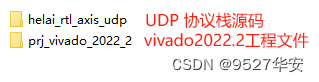

本设计基于88E1111使用纯verilog实现的1G-UDP 协议栈实现1G-UDP回环通信测试,之所以只用到了数据回环模式,是因为本设计旨在为用户提供一个可任意移植修改的1G-UDP协议栈架构,用户可通过此架构任意创建自己的项目,自由度和开放性极强;基于市面上88E1111占有率较高,且该PHY支持RGMII、GMII、SGMII三种模式,适应性极强的特点,本博创建了3套vivado2022.2版本的工程源码,分别如下:

本设计经过反复大量测试稳定可靠,可在项目中直接移植使用,工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字通信领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

我这里已有的以太网方案

目前我这里有大量UDP协议的工程源码,包括UDP数据回环,视频传输,AD采集传输等,也有TCP协议的工程,对网络通信有需求的兄弟可以去看看:直接点击前往