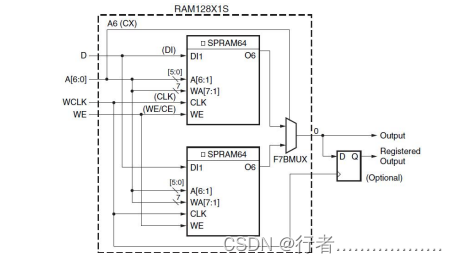

本文介绍: A:我本来只是随便回复了一个,数据用ram,控制用reg,对方回我说他知道,他想问什么时候用reg去实现ram功能,什么时候用sram。Q:逛论坛有人问,reg也可以实行sram的功能,且数据< 100bit的时候 ram的面积比reg实现的sram面积小,那在实现中如何选择?(3)sram作为静态存储,他的功耗,和reg的功耗不知道是怎么个对比,这个可能和sram从工艺上的实现方式有关。1)首先作为前端,我认为ram的实现方式是后端要关注的事情,在控制逻辑一样的情况下,选择面积较小的实现方式。

Q:set_property bitstream.config.timer_cfg 这样的配置用于哪里?

A:https://www.cnblogs.com/lazypigwhy/p/10450406.html

FPGA通过CPU远程升级方案_bitstream.config.timer_cfg-CSDN博客

Q:逛论坛有人问,reg也可以实行sram的功能,且数据< 100bit的时候 ram的面积比reg实现的sram面积小,那在实现中如何选择?

A:我本来只是随便回复了一个,数据用ram,控制用reg,对方回我说他知道,他想问什么时候用reg去实现ram功能,什么时候用sram。于是我就去找了一些资料,在找资料的过程当中觉得现在的搜索引擎容易误人子弟(误,这是我的问题)。下面开始回答。

1)首先作为前端,我认为ram的实现方式是后端要关注的事情,在控制逻辑一样的情况下,选择面积较小的实现方式。(Area)

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。