BGA引脚表示

1.1 FPGA此引脚要正确和清晰,会在“Package Pin”中用到次物理接口

1.2, MCU 只用管对应的GPIO逻辑接口就可以了

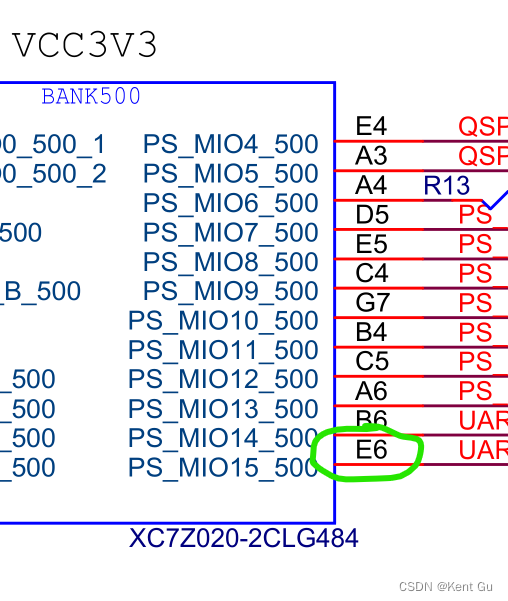

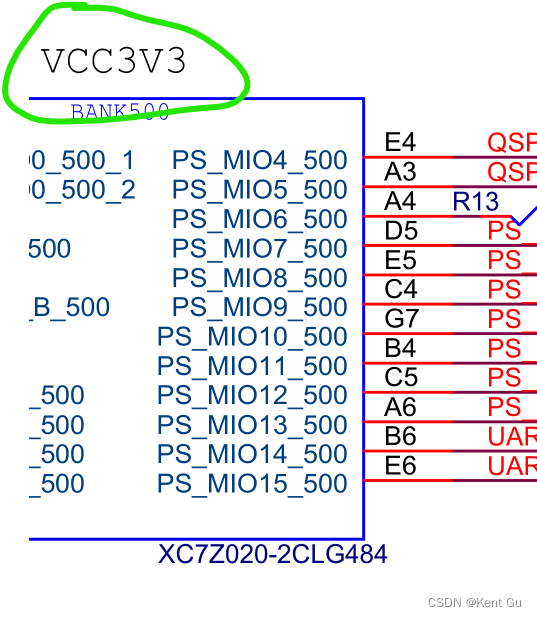

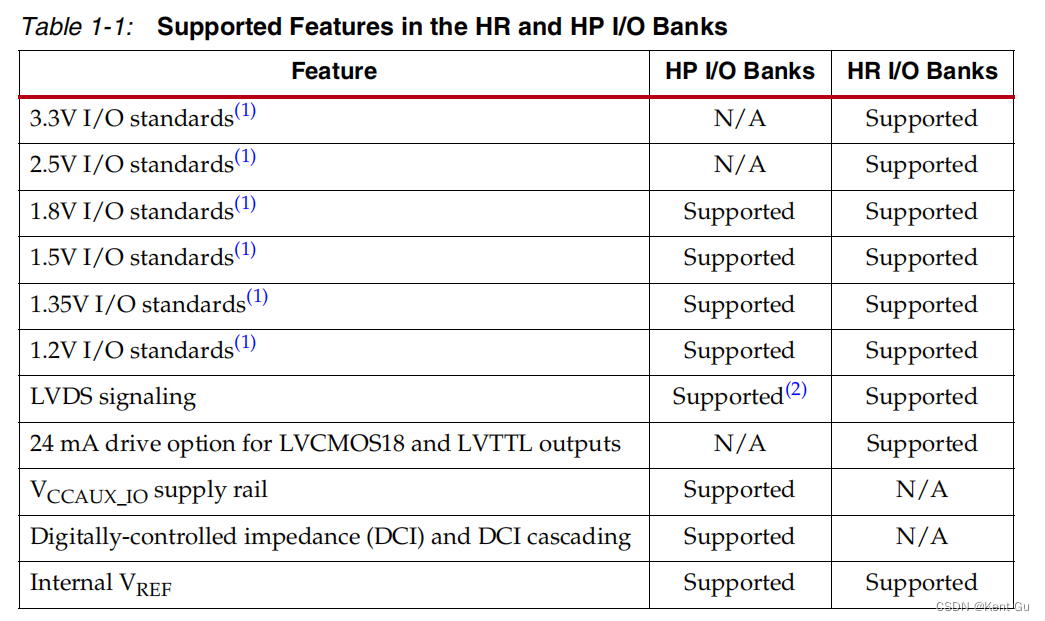

标识Bank电平

标识出对应Bank的电平,在电路设计中可以清晰的知道对应的脚位输出电平。在”IO std”也方便的选择

Each device is split into I/O banks to allow for flexibility in the choice of I/O standards (see

UG471

Bank & 引脚

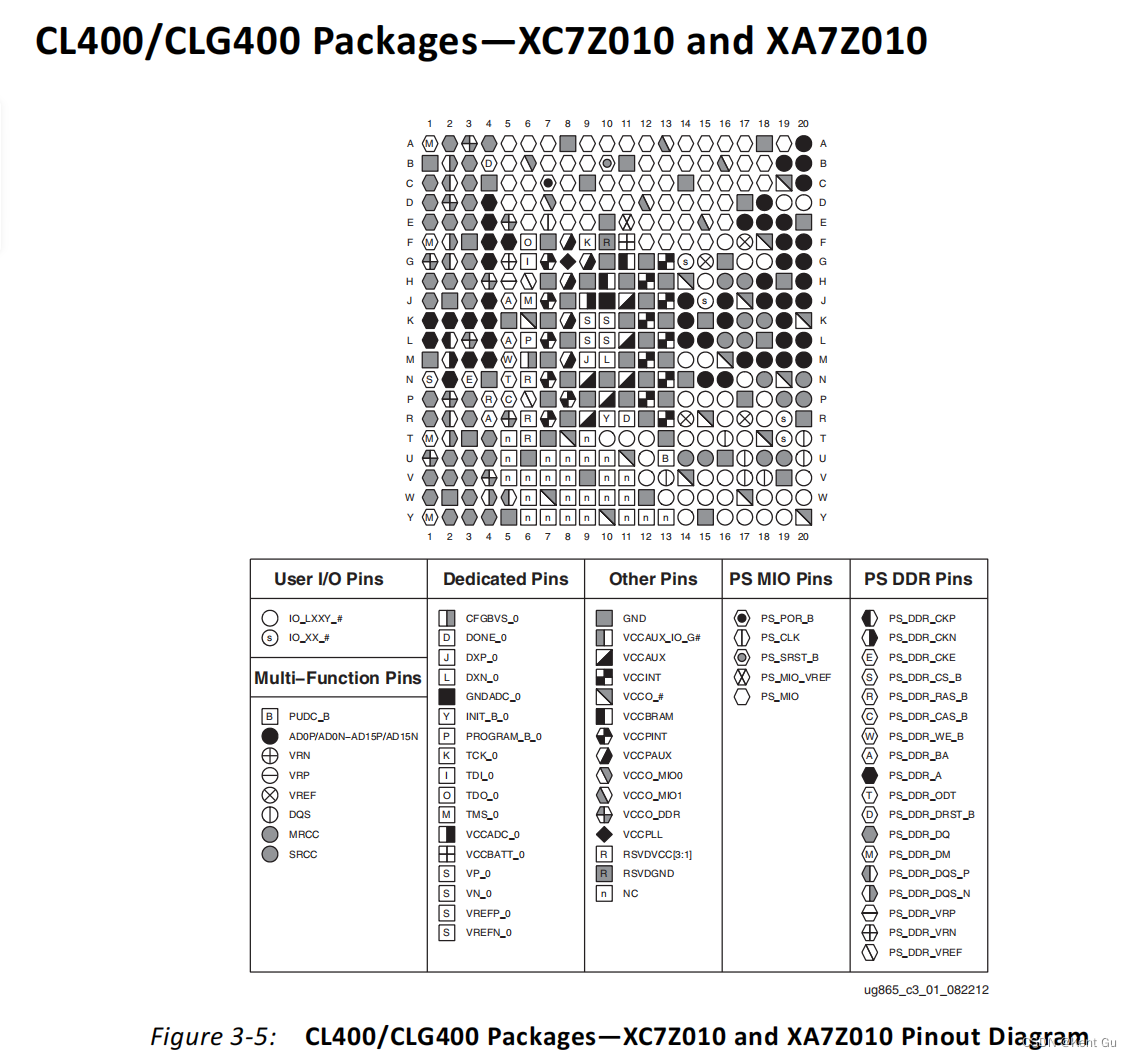

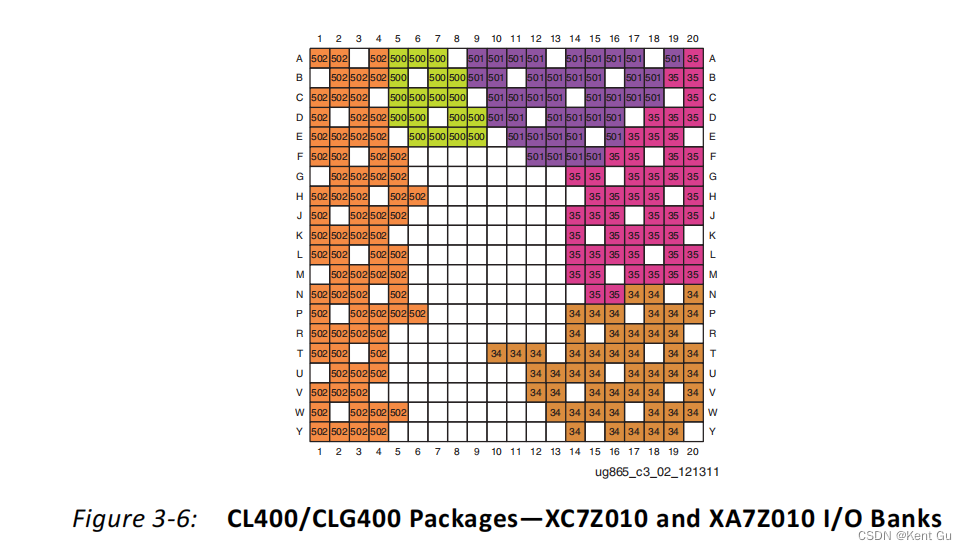

3.1 Package and PinOut

可以利用“WindowsPackage”程序反推硬件引脚旋转

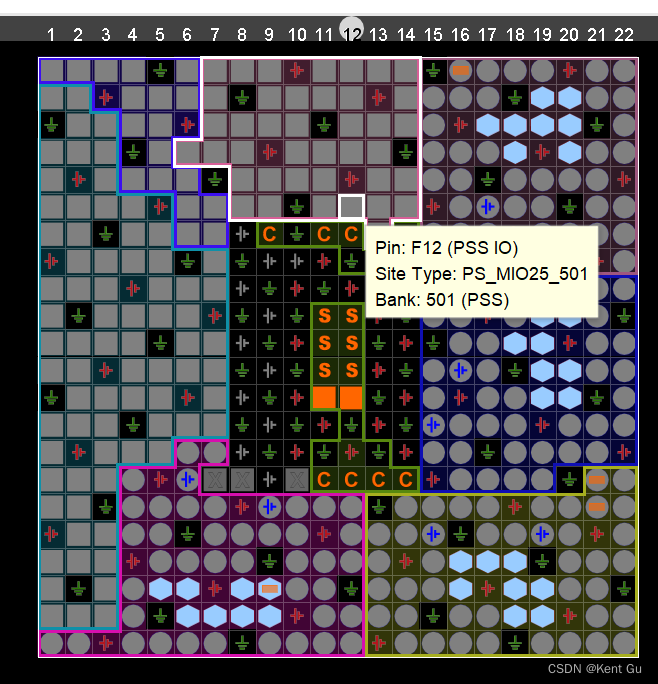

Device Diagram

Bank划分原则

一旦Bank引脚电平确定,那么整个Bank对应的bank上的IO逻辑就确定了。有的时候可以设置Bank电压可选择的如下图。

原文地址:https://blog.csdn.net/weixin_39305628/article/details/135593234

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。

如若转载,请注明出处:http://www.7code.cn/show_57202.html

如若内容造成侵权/违法违规/事实不符,请联系代码007邮箱:suwngjj01@126.com进行投诉反馈,一经查实,立即删除!