本文介绍: Tsu裕量 = (Tskew + 时钟周期 – Tsu) – (Tco + Tdelay)Thd裕量 = Tco + Tdelay – Thd。时间分析,还要考虑数据变化的建立时间与保持时间。两个时间都大于0,才能保证系统不产生亚稳态。建立时间裕量、组合逻辑延时决定时钟最高频率。后缀L的这个单元中,会生成锁存器。一级逻辑级数延迟约为0.4ns。3.查看详细计算过程。

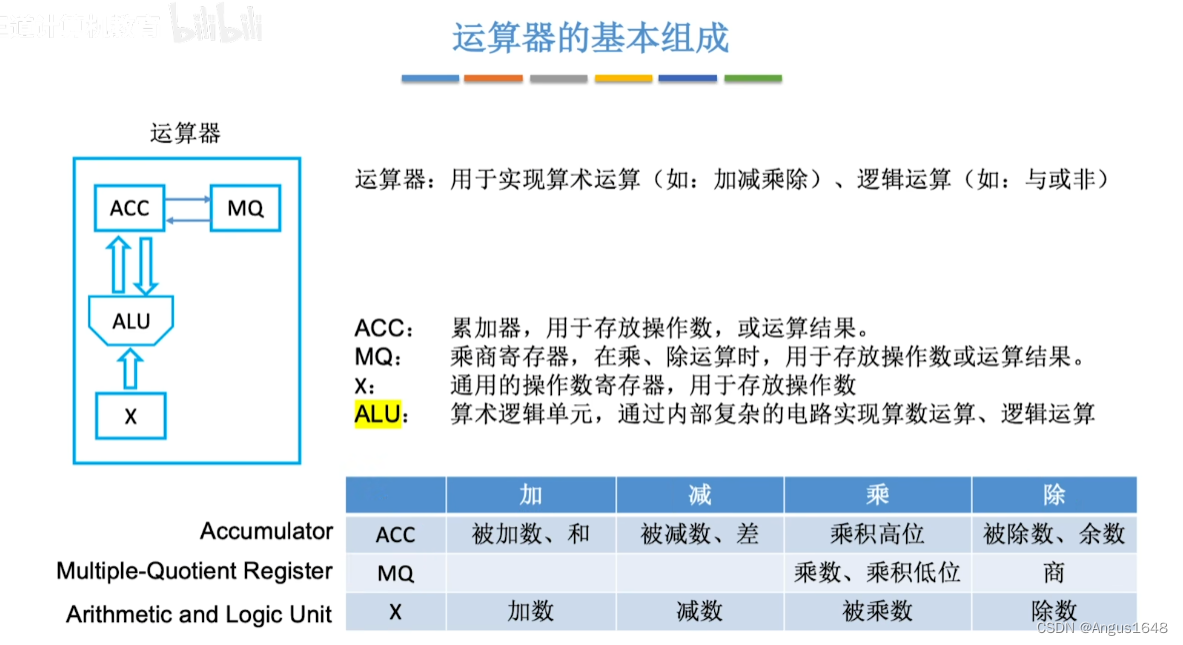

(1)内部资源

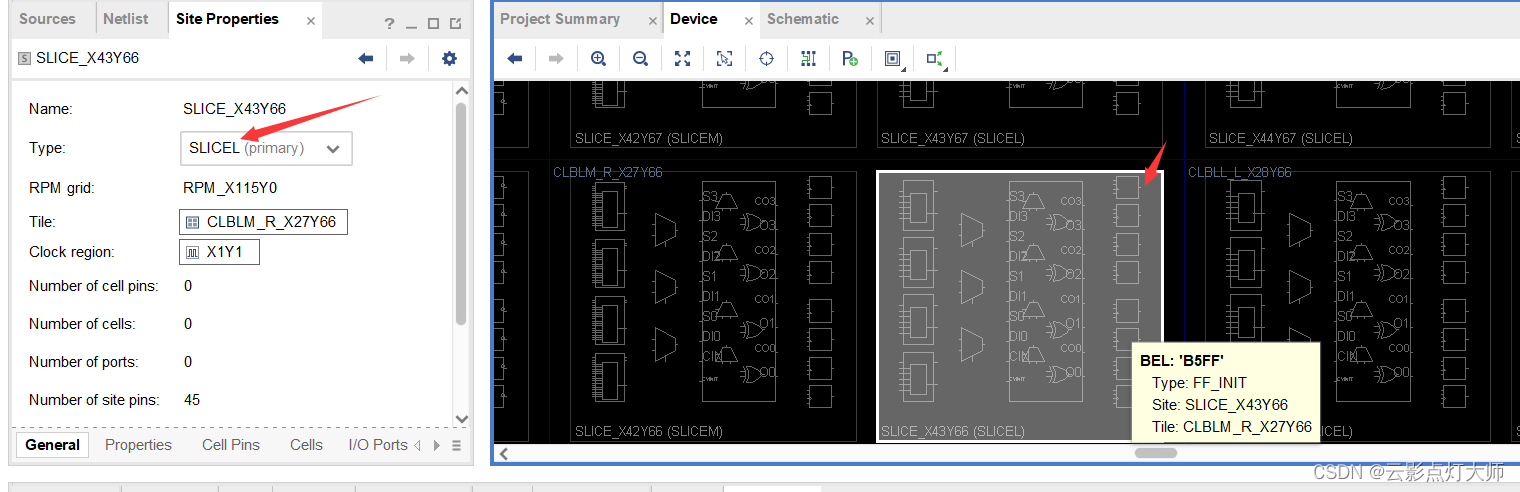

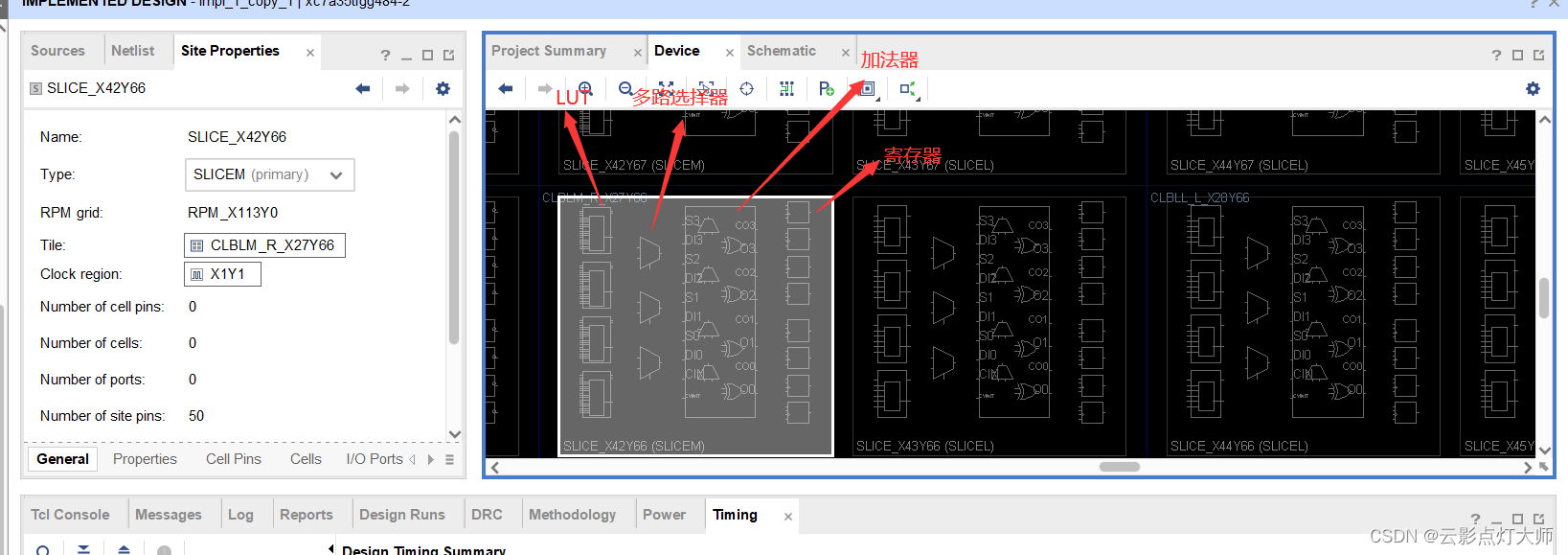

后缀L的这个单元中,会生成锁存器

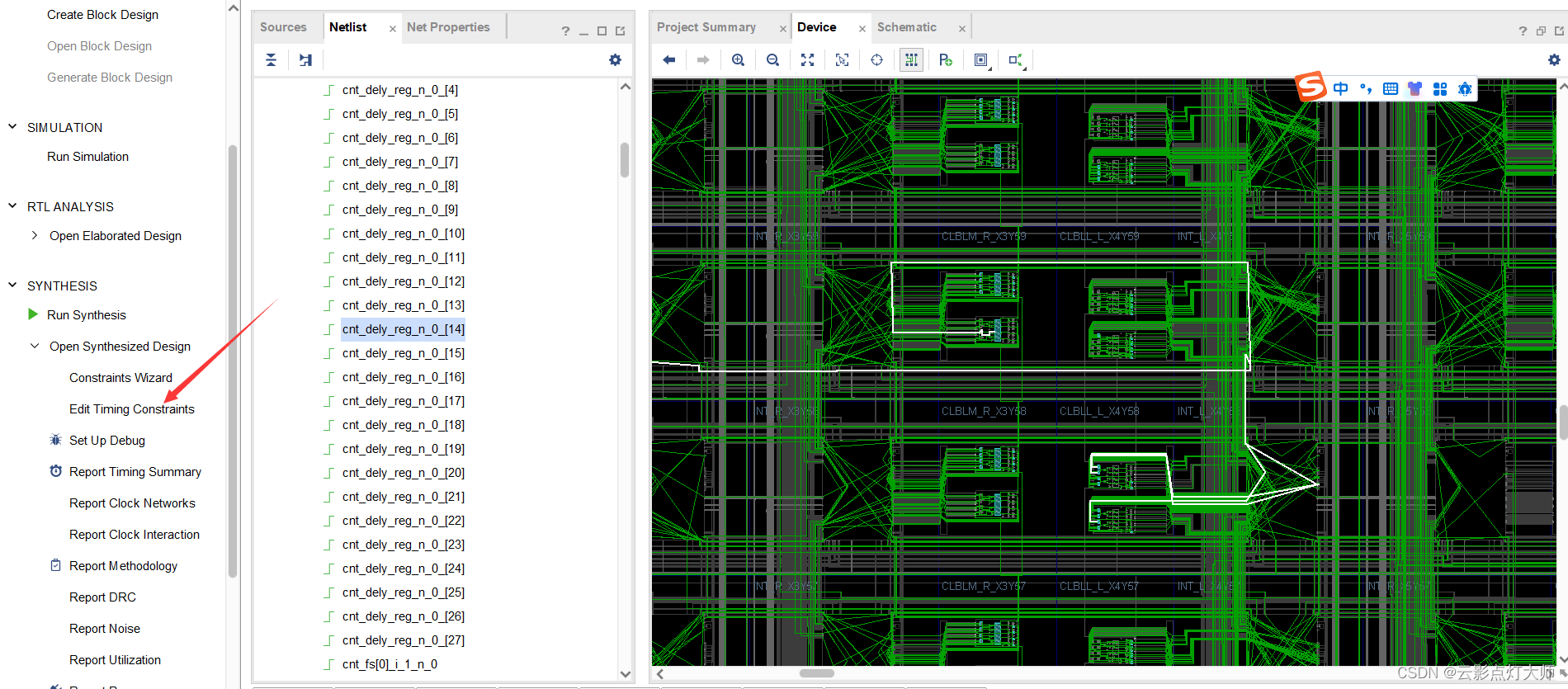

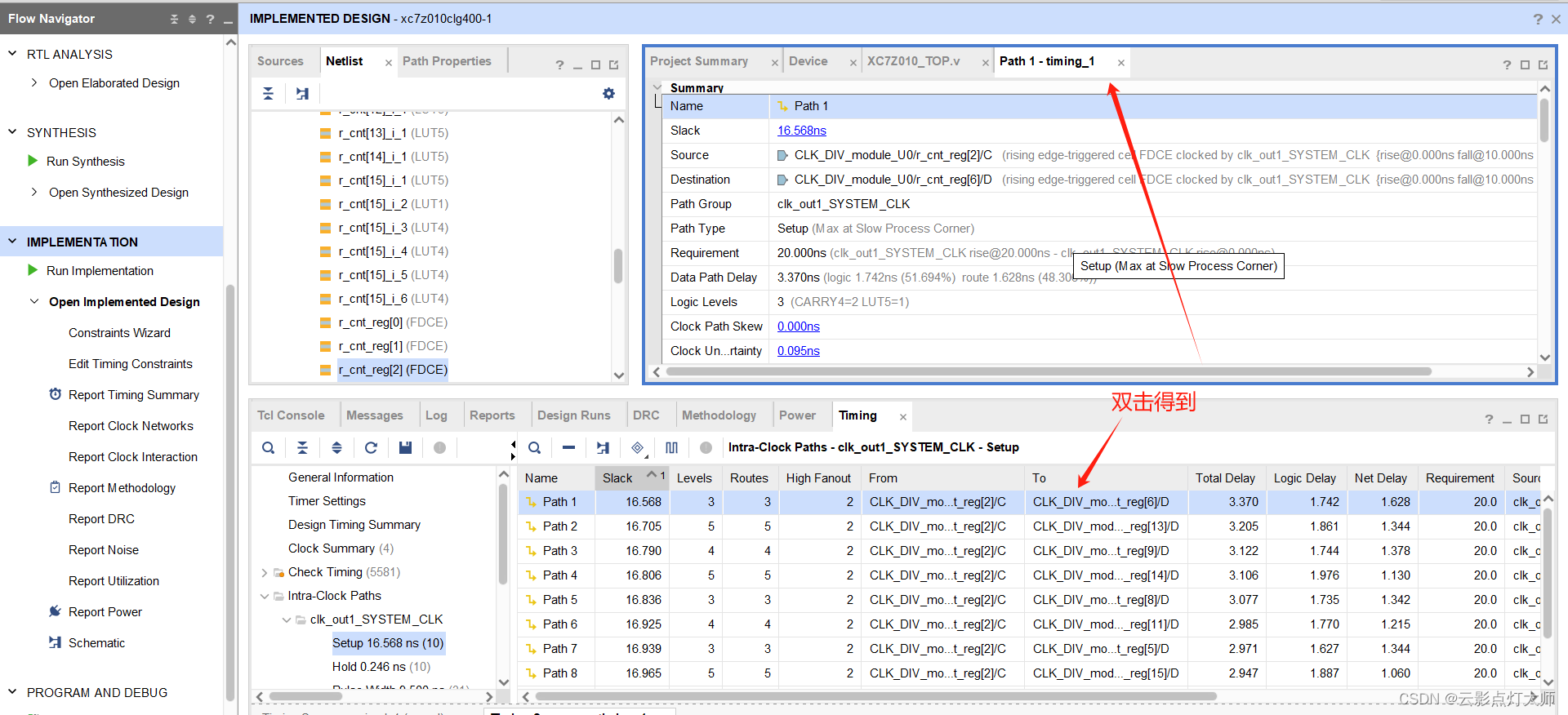

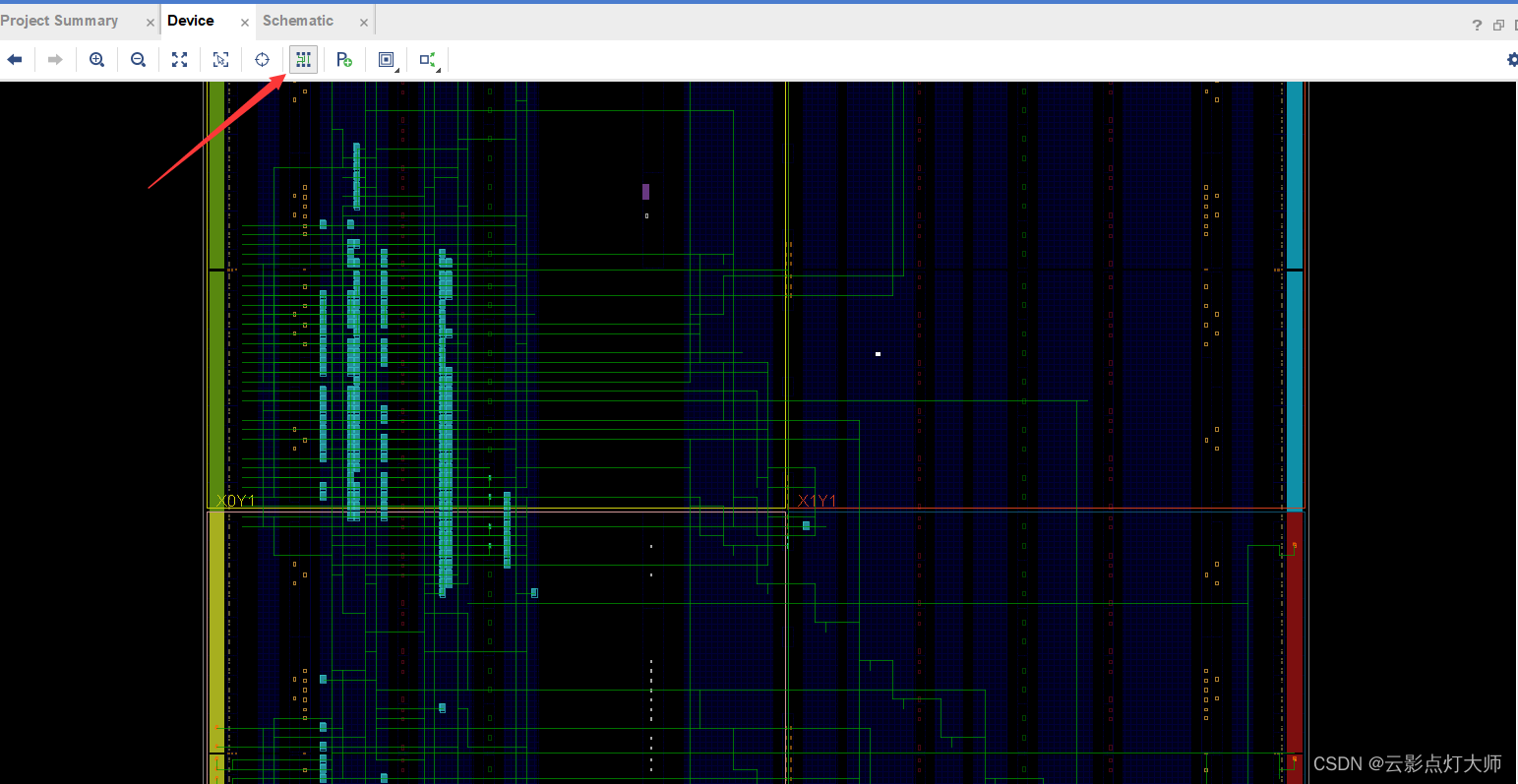

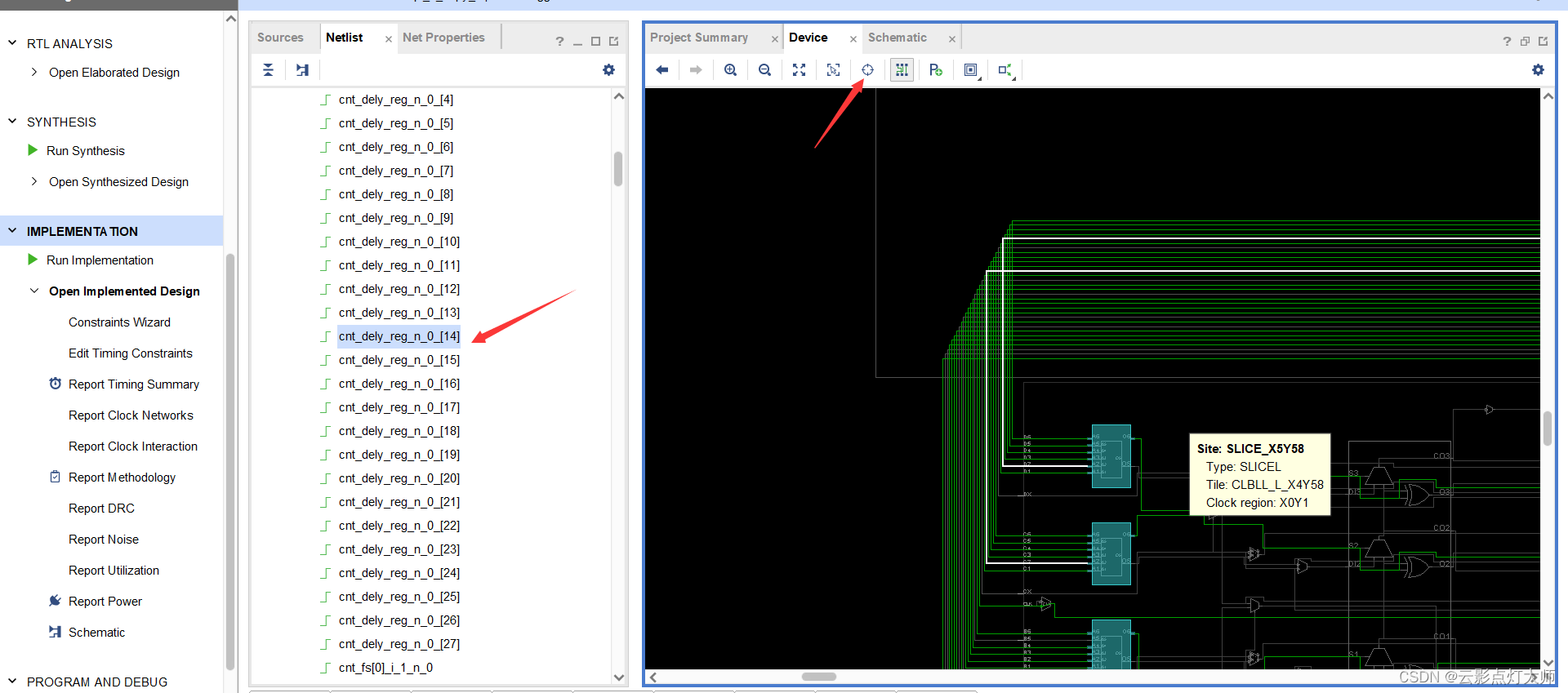

查看布线

定位线路

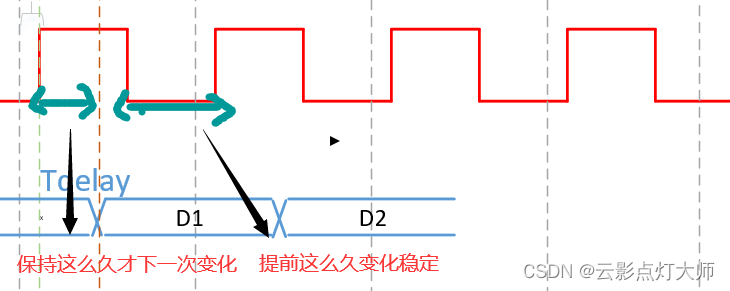

(2)传输模型分析(寄存器到寄存器)

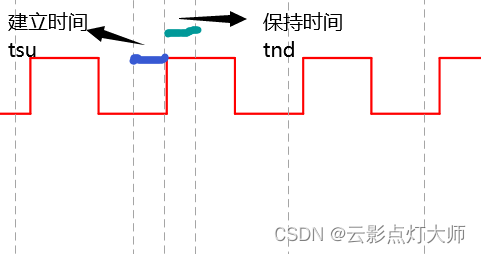

时间分析,还要考虑数据变化的建立时间与保持时间

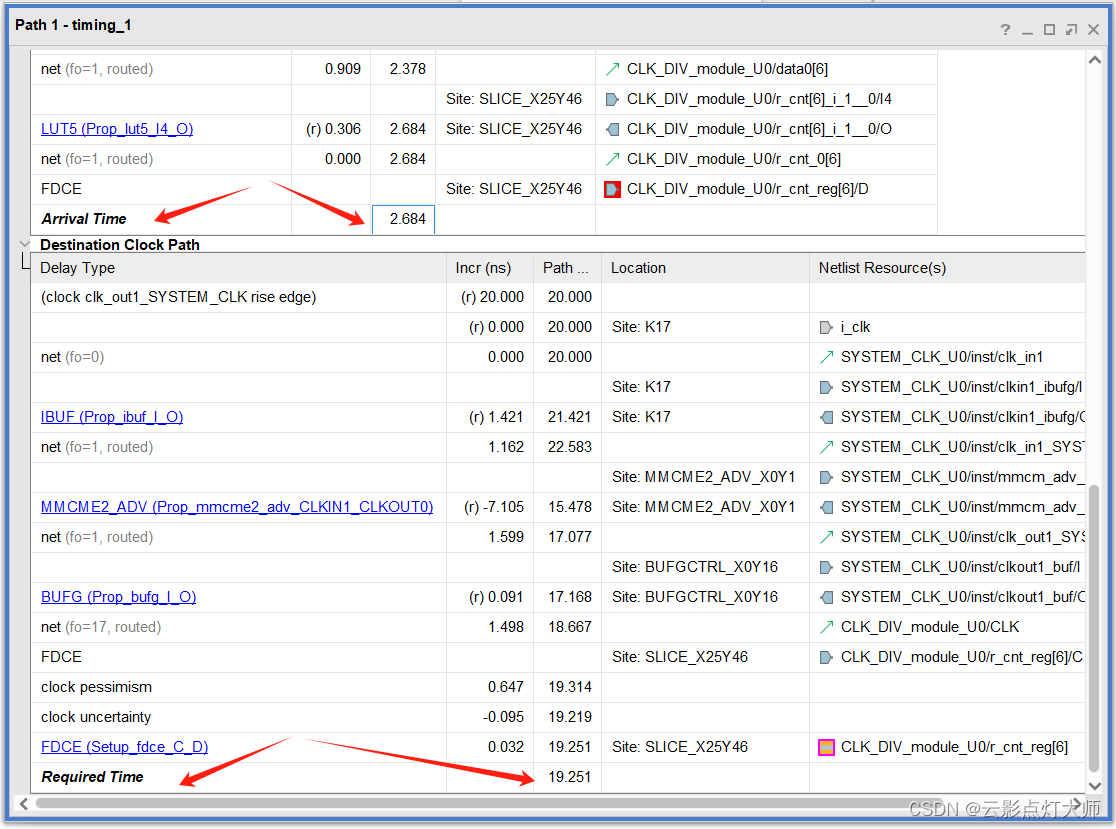

经过图上计算可得公式 :

Tsu裕量 = (Tskew + 时钟周期 – Tsu) – (Tco + Tdelay)

Thd裕量 = Tco + Tdelay – Thd

两个时间都大于0,才能保证系统不产生亚稳态。

建立时间裕量、组合逻辑延时决定时钟最高频率

一级逻辑级数延迟约为0.4ns

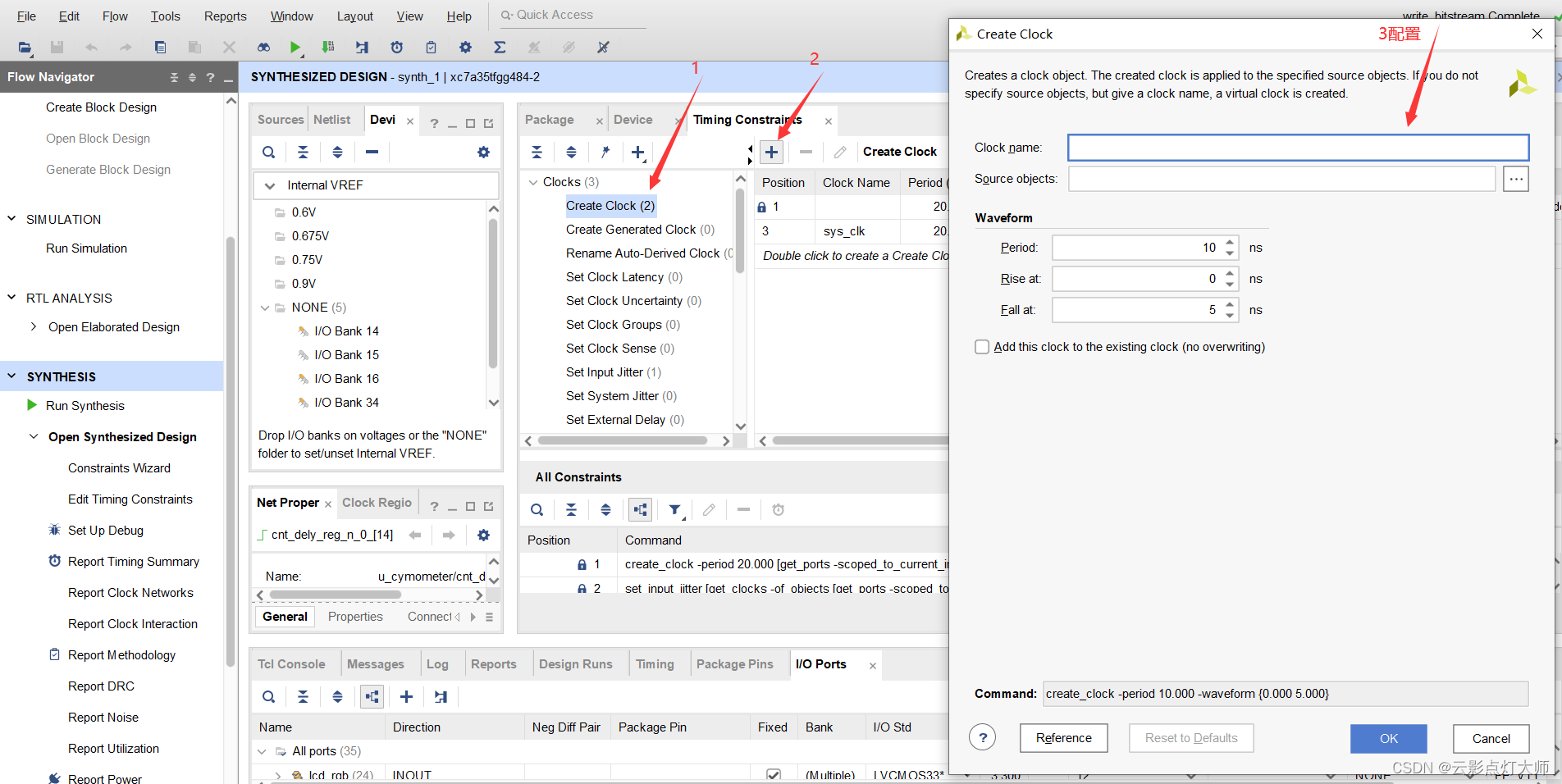

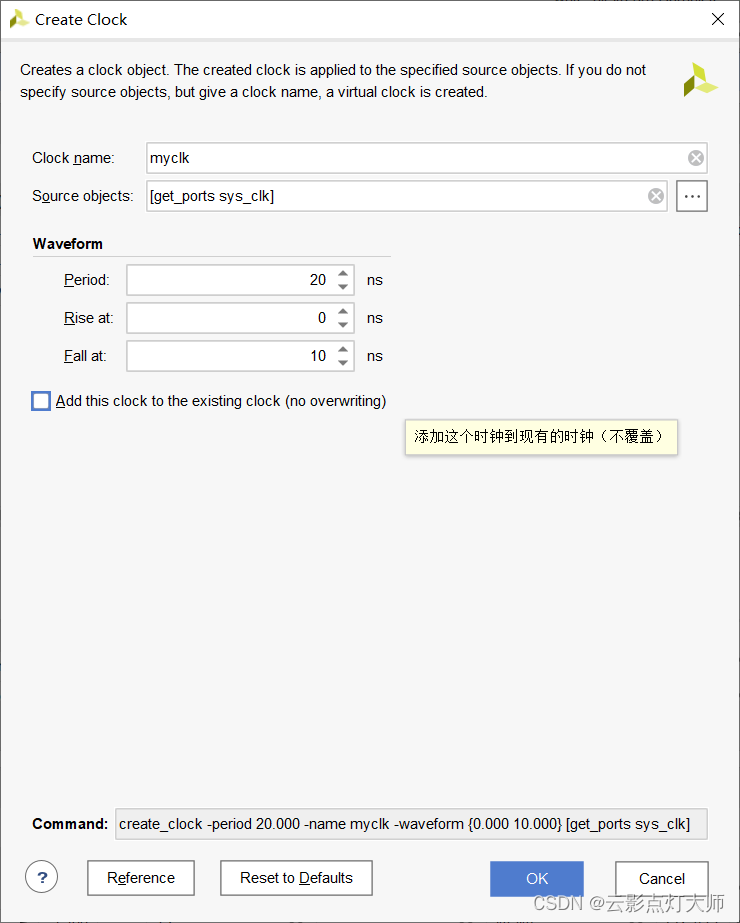

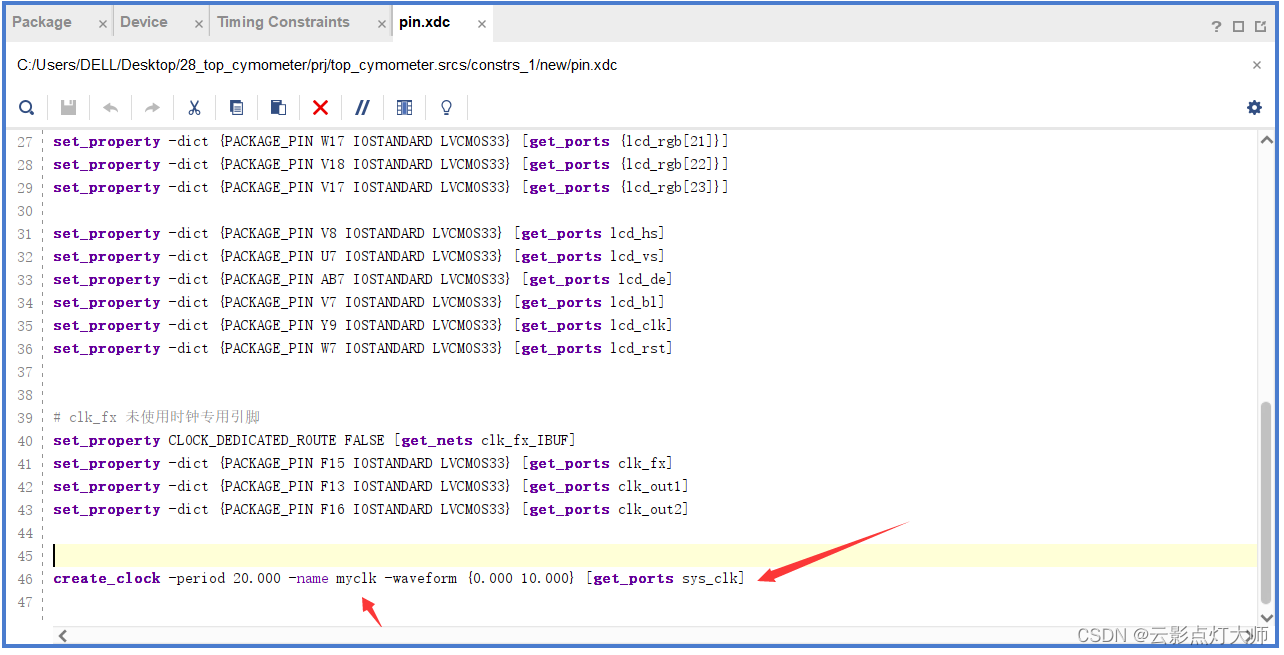

(3)时序约束操作

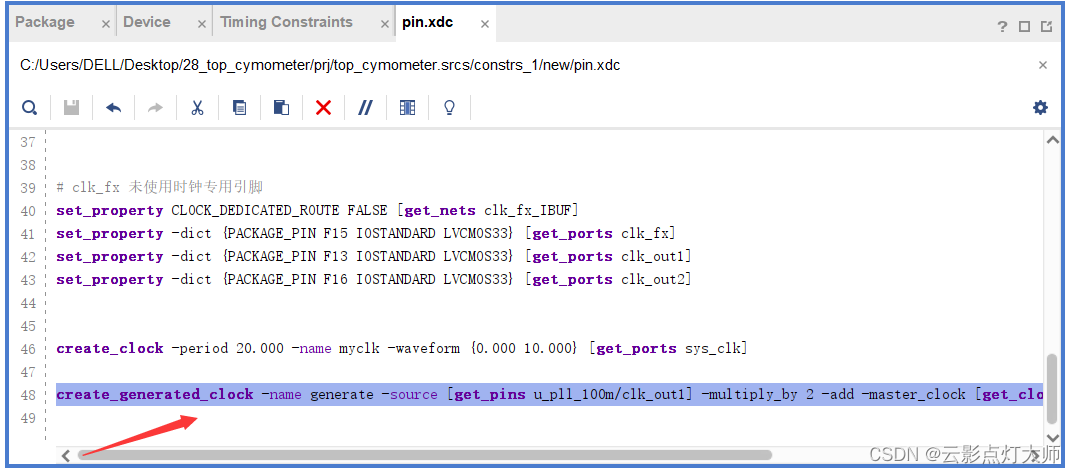

1 约束主时钟

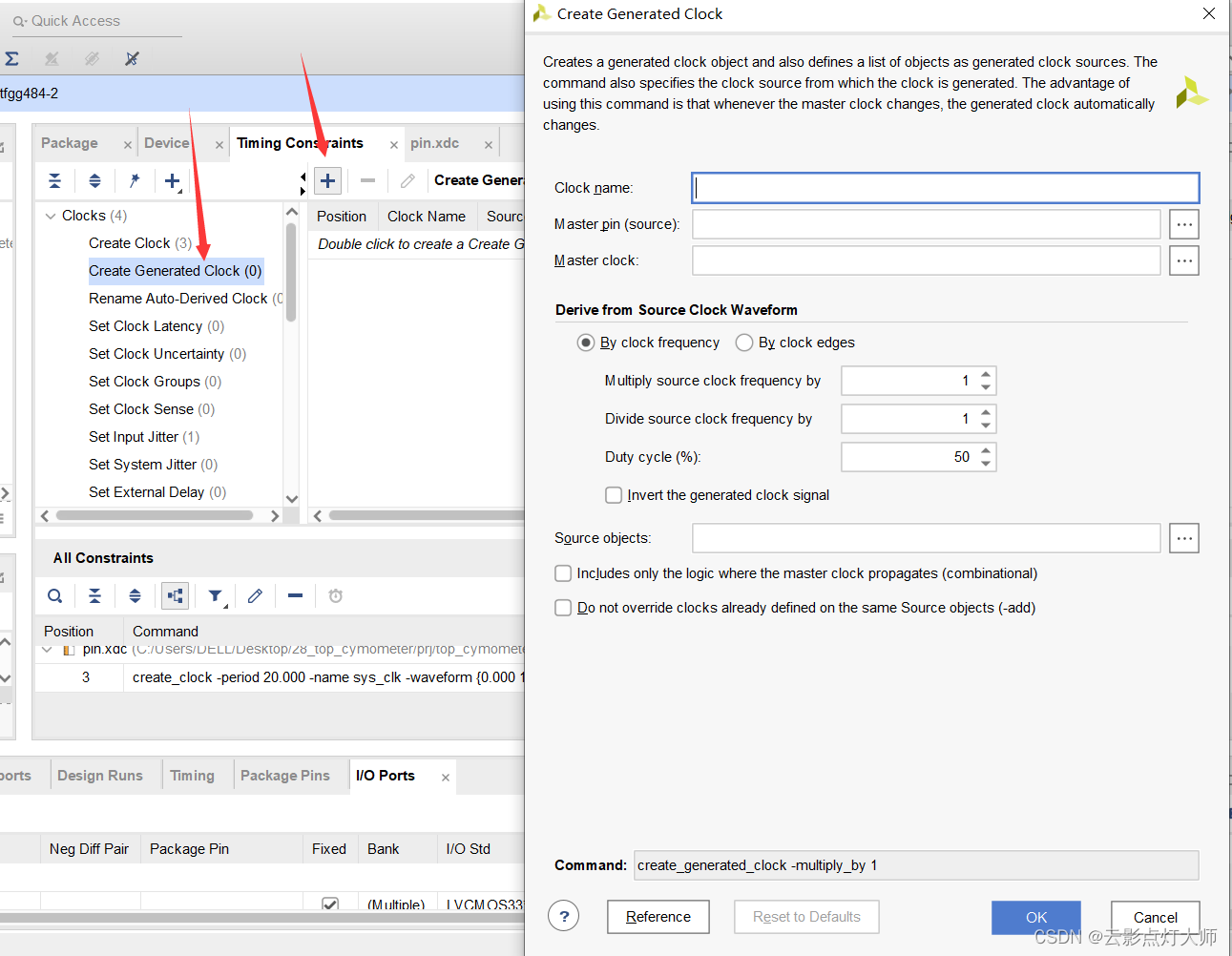

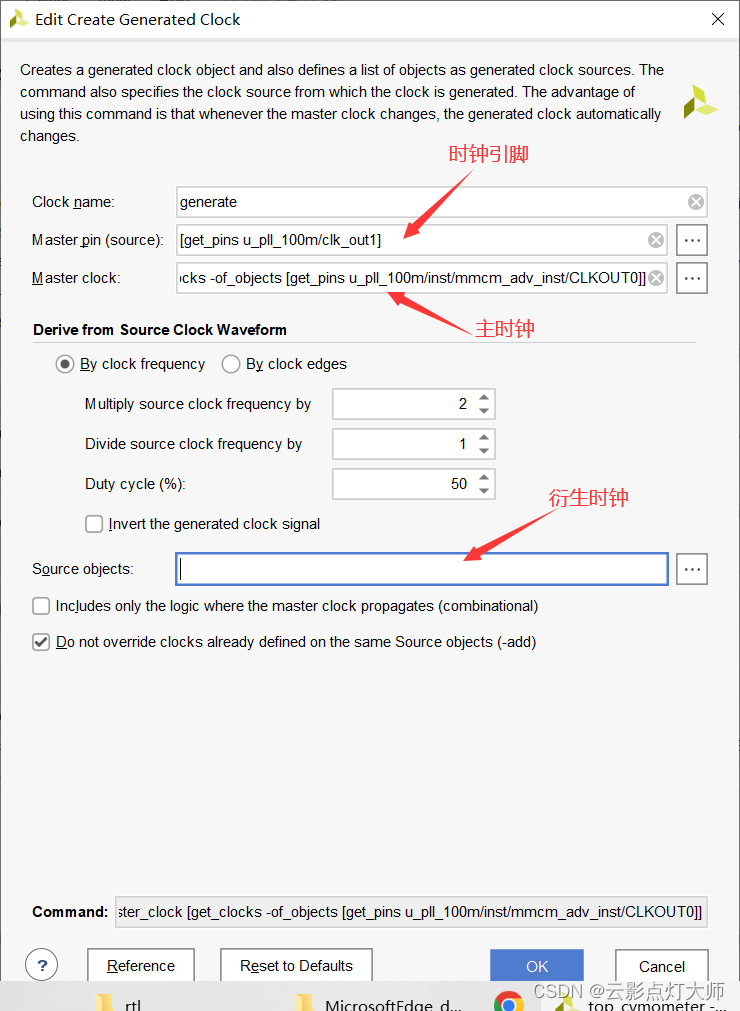

2 约束衍生时钟

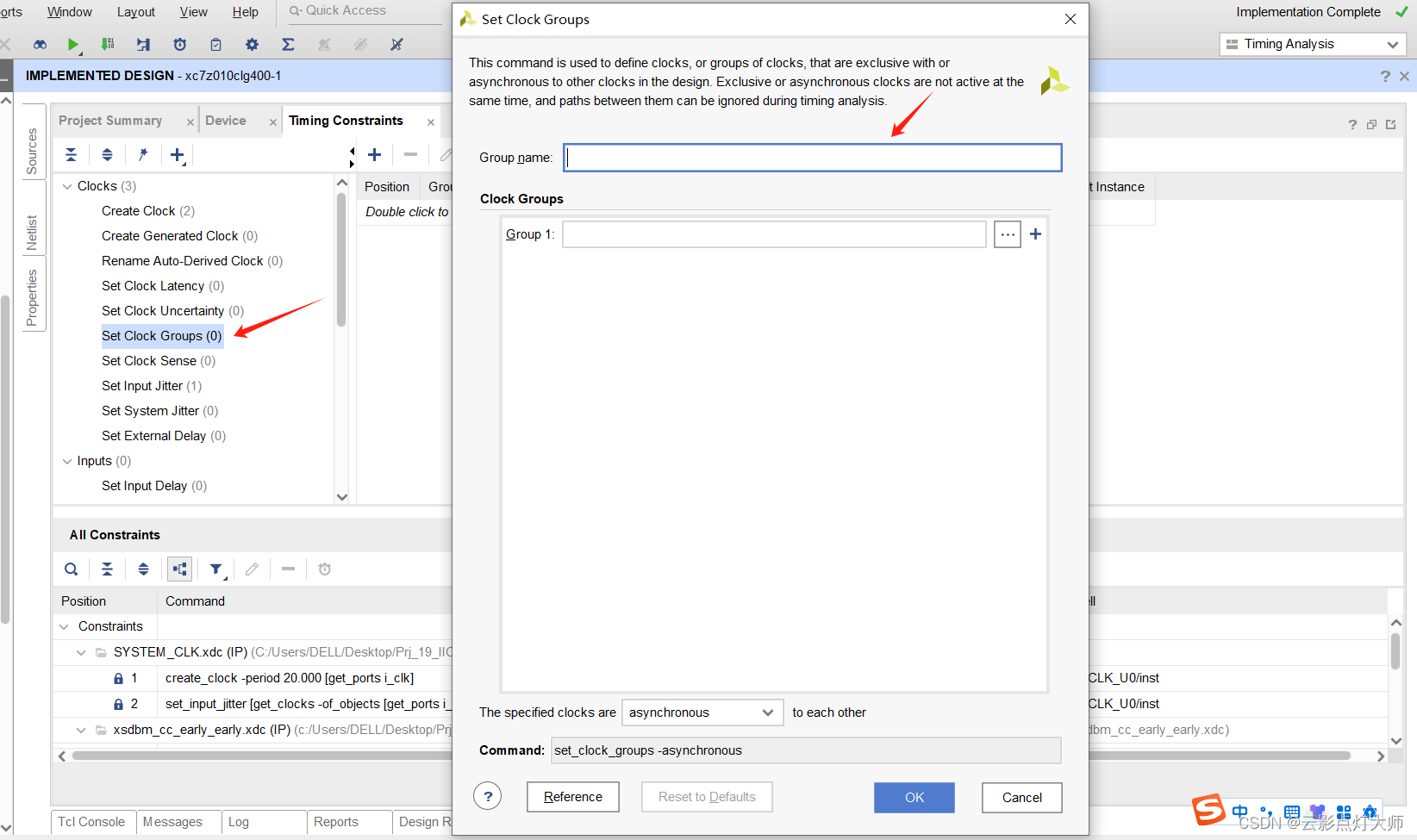

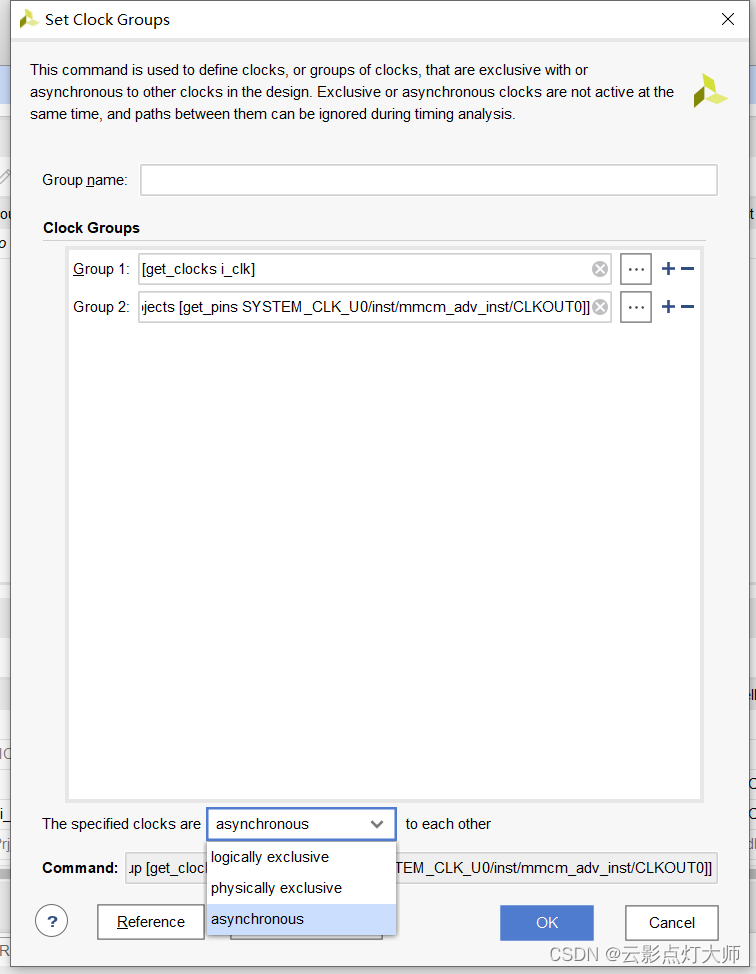

3 设置时钟组

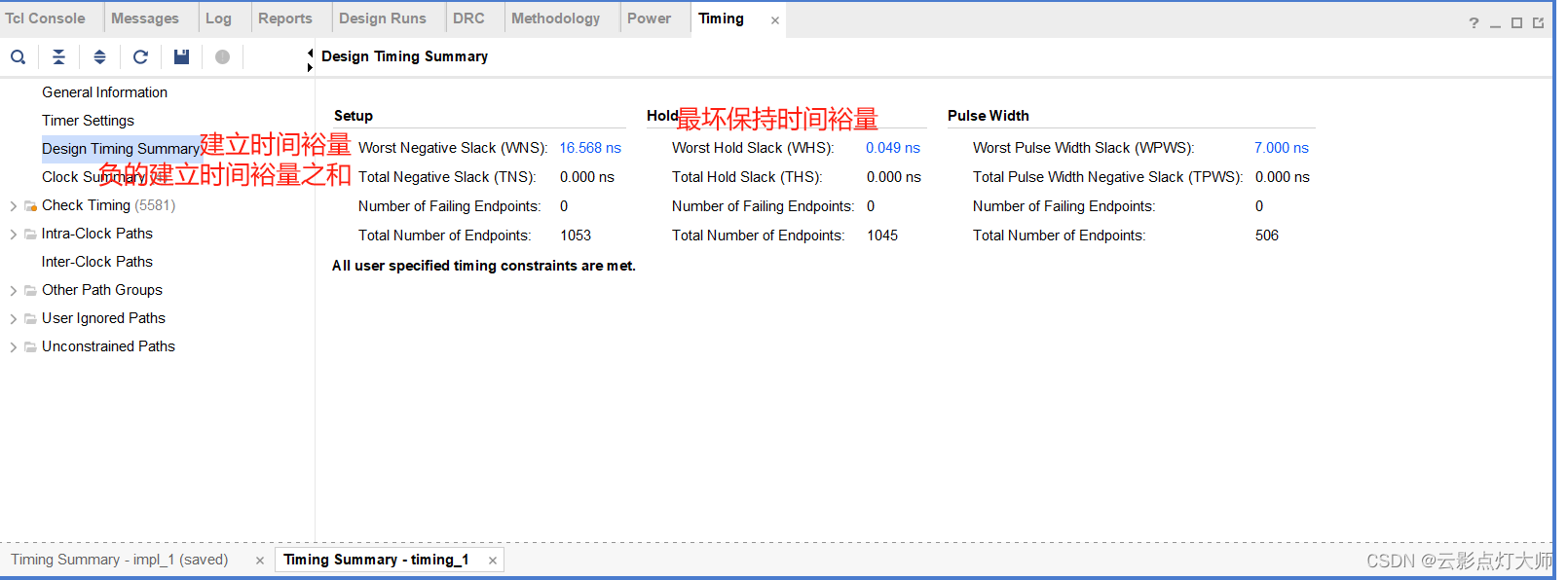

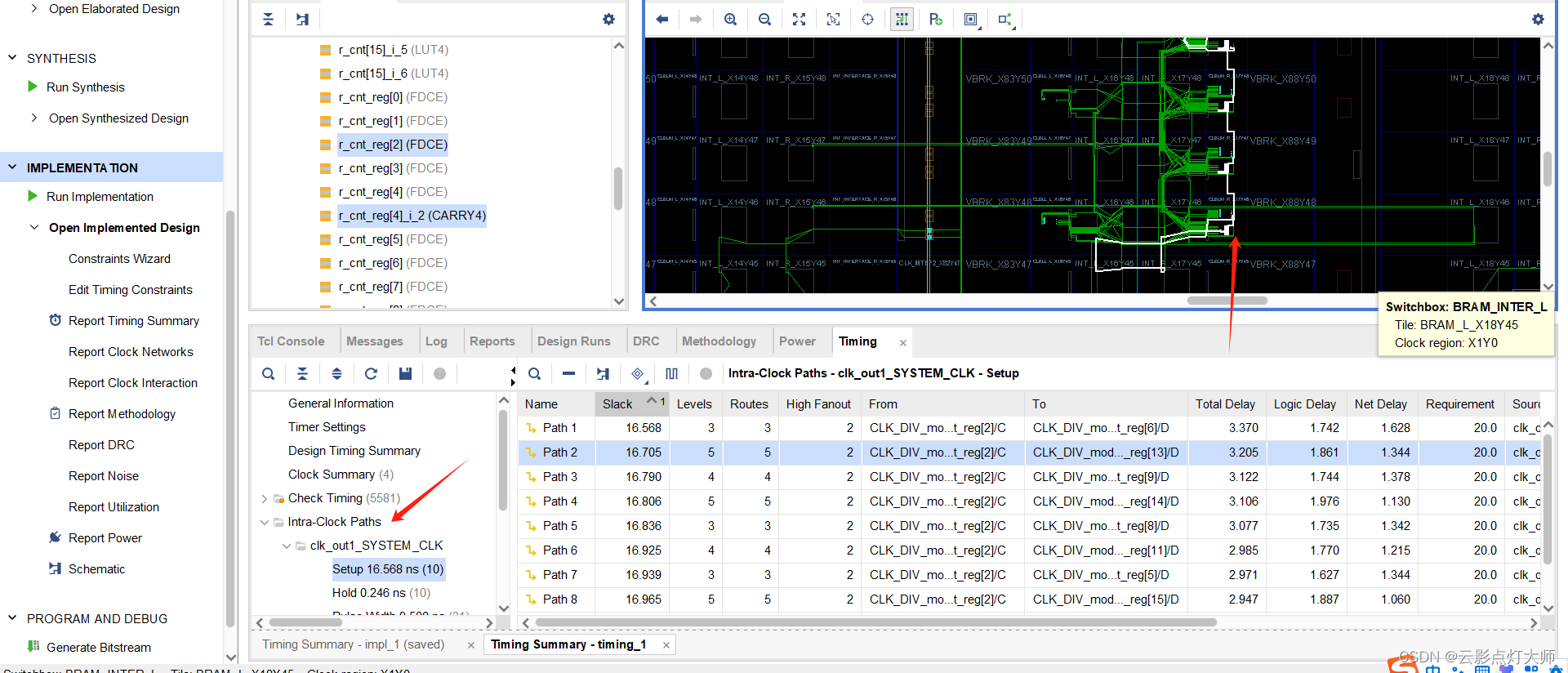

(4)查看报告

声明:本站所有文章,如无特殊说明或标注,均为本站原创发布。任何个人或组织,在未征得本站同意时,禁止复制、盗用、采集、发布本站内容到任何网站、书籍等各类媒体平台。如若本站内容侵犯了原著者的合法权益,可联系我们进行处理。