链接:https://pan.baidu.com/s/1E4x2TX_9SYhxM9sWfnehMg?pwd=1688

提取码:1688

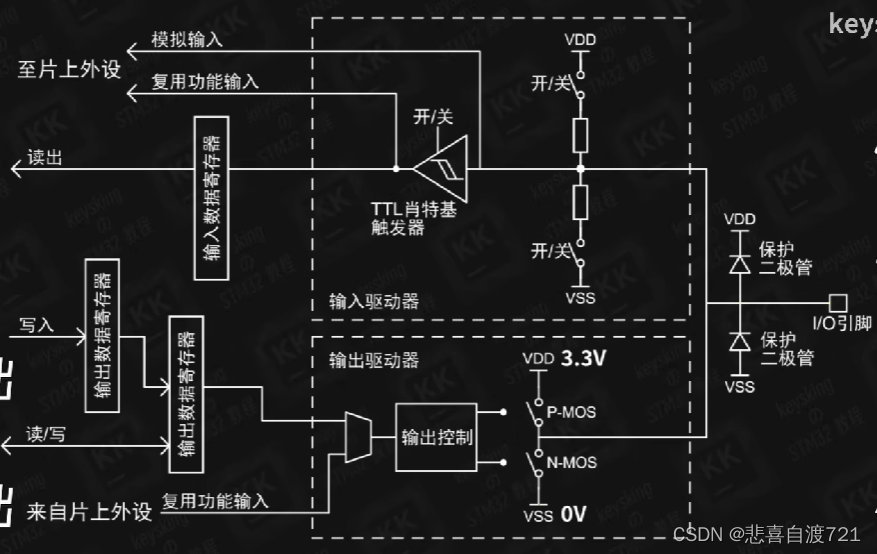

上午:ARM的I/O口

下午:ARM的时钟设定

教学内容:

1、S3C2440的I/O口

S3C2440A共有289个管脚,其中130个可配置为多功能复用输入/输出口,共分为9组,即PORTA~PORTH、PORTJ按照位数的不同,可分为:

—PORTA(GPA):23位输出口;

—PORTB(GPB):11位输入/输出口;

—PORTC(GPC):16位输入/输出口;

—PORTD(GPD):16位输入/输出口;

—PORTE(GPE):16位输入/输出口;

—PORTF(GPF):08位输入/输出口;

—PORTG(GPG):16位输入/输出口;

—PORTH(GPH):11位输入/输出口;

—PORTJ (GPJ): 13位输入/输出口;

对于I/O的控制,一般由GPGCON和GPGDAT和GPGUP三种寄存器控制,其中:

GPGCON:为I/O的设置,可以设置为00=输入,01=输出,10=允许中断,11=保留

GPGDAT:和I/O口交流的数据寄存器,读写都是对GPGDAT操作

GPGUP:设置是否上拉电阻,0:设置;1:不设置

例如:

GPGCON的地址是0x56000060,可读可写,复位后默认为0

程序设计,例如:

//***********************************************

#include “2440addr.h” //声明S3C2440的寄存器及其常用变量

#include “2440lib.h”

#include “uart.h”

#define GPGCON (*(volatile unsigned long *)0x56000060) //不可优化,为UL型

#define GPGUP (*(volatile unsigned long *)0x56000068)

#define GPGDAT (*(volatile unsigned long *)0x56000064)

GPGCON &=~(0x03<<0*2)|(0x03<<1*2)|(0x03<<2*2); //利用移位对GPGCON设置

GPGCON |=(0x01<<0*2)|(0x01<<1*2)|(0x01<<2*2);

//rGPGCON &=~(0x03<<0*2)|(0x03<<1*2)|(0x03<<2*2); //不需要前面的#define,用的是2440addr.h的头文件声明

//***********************************************************

2、时钟和电源

S3C2440的时钟可以选用晶振(XTAL),也可以使用外部时钟(EXTCLK),由系统复位时,在复位信号上升沿对引脚OM3、OM2所测的状态来确定。其对应关系如下表所示:

对时钟而言,晶振的频率一般不能高于100M,而对于现在的嵌入式芯片而言,速度越来越快,为了获得更高的频率可以采用锁相环和选频技术从而获得更高的频率,ARM9的具体时钟实现如下:

从1,2可知,通过OM[3:2]选择时钟信号来源,第3是含有两个锁相环MPLL、UPLL,它们分别产生系统所需要的时钟MPLL:FCLK—CPU,HCLK—AHB总线,PCLK—APB总线;UPLL: 产生UCLK供USB(48MHz)和Camera;

1)、对于系统上电开始,PLL是没有启动的,所以FCLK=Fin(晶振频率);

2)、设置MPLL几个寄存器后,等待一定时间,MPLL才能输出稳定,之后才能使用;

3)、(LOCKTIME寄存器)等待时间一般不要设定,使用默认时间即可;

MPLLCON:设置MPLL锁相环的输出频率

UPLLCON:设置UPLL锁相环的输出频率

CLKCON:控制所有设备的时钟关开,睡眠,空闲模式的设定

CLKSLOW:慢模式下的相关设置

CLKDIVN:分频设置UCLK,HCLK,PCLK的频率

对于正常模式,只要一般只要设置MPLLCON和CLKDIVN,CPU频率FCLK=MPLLCLK

例如:

//*********************************************

//设置MPLL锁相环的输出频率

void ChangeMPllValue(int mdiv,int pdiv,int sdiv)

{

rMPLLCON = (mdiv<<12) | (pdiv<<4) | sdiv;

}

//设置HCLK和PCLK

void ChangeClockDivider(int hdivn_val,int pdivn_val)

{

int hdivn=2, pdivn=0;

switch(hdivn_val)

{

case 11: hdivn=0; break;

case 12: hdivn=1; break;

case 13:

case 16: hdivn=3; break;

case 14:

case 18: hdivn=2; break;

}

switch(pdivn_val){

case 11: pdivn=0; break;

case 12: pdivn=1; break;

}

rCLKDIVN = (hdivn<<1) | pdivn;

switch(hdivn_val) {

case 16: break;

case 18: break;

}

}

//**********************************************